# **NutoChips**

# AC781x Reference Manual

Version: 1.2 Release date: 2022-01-06

© 2013 AutoChips Inc.

This document contains information that is proprietary to AutoChips Inc. Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

Specifications are subject to change without notice.

# **VutoChips**

# **Document Revision History**

| 1.1     2021-06-16     AutoChips     1. Add description of whi chapter 1.1 and 9.1       2.     Add description of MPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ter bit attribute from R to RW<br>ich UART module supporting LIN in<br>in chapter2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1     2021-06-16     AutoChips     1.     Add description of whi<br>chapter 1.1 and 9.1       2.     Add description of MPU       3.     Update option byte end                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ter bit attribute from R to RW<br>ich UART module supporting LIN in<br>in chapter2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| chapter 1.1 and 9.1<br>2. Add description of MPU<br>3. Update option byte end                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | in chapter2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <ul> <li>4. Add description of Chip</li> <li>5. Add description of Chip</li> <li>6. Update the description of T.5</li> <li>7. Change description for U</li> <li>9. Modify the register of bit</li> <li>10. Modify the description of</li> <li>11. Update the description of ADC</li> <li>13. Modify mode5 sequence</li> <li>14. Modify "timer channel" to</li> <li>15. Modify "timer channel" to</li> <li>16. Update the description of</li> <li>17. 5</li> <li>18. Add description of typics</li> <li>in chapter 17.5</li> <li>19. Modify the description of</li> <li>19.14</li> <li>20. Update the description of</li> <li>20.4</li> <li>23. Modify the description of</li> <li>20.4</li> <li>23. Modify the description of</li> <li>24. Add the description of</li> <li>25. Add description of</li> <li>26. Add the description of</li> <li>27. Add the description of</li> <li>28. Add the description of</li> <li>29. Add the description of</li> <li>20.4</li> <li>23. Modify the description of</li> <li>20.4</li> <li>23. Modify the description of</li> <li>24. Add the description of</li> <li>25. Add description of</li> <li>26. Add the description of</li> <li>27. Add the description of</li> <li>28. Add the description of</li> <li>29. Add the description of</li> <li>20.6</li> <li>25. Add description of "The modify searches" in chapter 23.1.2</li> </ul> | of RS485 delay in chapter 9.12<br>for IDLE flag in chapter 9.12<br>conversion format in chapter 10<br>e figure error in chapter 10.3<br>description in chapter 12<br>o "timer" in chapter 14<br>of GPIO_ODR register in table 17-5<br>of GPIO_E4_E2 register in chapter<br>cal value for pull-up, pull-down resistor<br>ue of SPI_CFG1 register in chapter<br>of SPI_STATUS register in chapter<br>of DMA operation mode in chapter<br>of DMA_MEM_END_ADDR register in<br>of disable DMA in circular mode in<br>ninimum programming bit width is 32<br>ing address needs to be aligned with 4 |

© 2013 - 2021 AutoChips Inc.

|     |            |           |     | bit in chapter 23.5                                       |

|-----|------------|-----------|-----|-----------------------------------------------------------|

| 1.2 | 2022-01-06 | AutoChips | 1.  | Add description of ISP download pin in chapter 2.3 11     |

|     |            |           | 2.  | Modify description of BUSOFF bit in chapter 7.4           |

|     |            |           | 3.  | Add description of UART baud rate range in chapter 9.2    |

|     |            |           | 4.  | Add chapter 12.3.11 for PWM registers updated from write  |

|     |            |           |     | buffers                                                   |

|     |            |           | 5.  | Add chapter 12.3.22 for PWM features priority             |

|     |            |           | 6.  | Add chapter 17.3 for GPIO block diagram                   |

|     |            |           | 7.  | Add description of SPI baud rate range in chapter 19.2    |

|     |            |           | 8.  | Add description of SPI TXEIO, RXFIE in chapter 19.14      |

|     |            |           | 9.  | Update description of DMA priority in chapter 20.5.2      |

|     |            |           | 10. | Update description of DMA end address in chapter 20.5.3.3 |

|     |            |           |     | and chapter 20.6                                          |

# **NutoChips**

# Legal Notice

This reference manual contains information that is confidential to AUTOCHIPS Inc. Unauthorized use or disclosure of the information contained herein is prohibited. You may be held responsible for any loss or damages suffered by Autochips Inc. for your unauthorized disclosure hereof, in whole or in part.

Information herein is subject to change without noticed. AUTOCHIPS Inc. does not assume any responsibility for any use of, or reliance on, the information contained herein.

THIS REFERENCE MANUAL AND ALL INFORMATION CONTAINED HEREIN IS PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, WHETHER EXPRESS, IMPLIED, STATUTORY, OR OTHERWISE. AUTOCHIPS INC. SPECIFICALLY DISCLAIMS ALL IMPLIED WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, AND FITNESS FOR A PARTICULAR PURPOSE. NEITHER DOES AUTOCHIPS INC. PROVIDE ANY WARRANTY WHATSOEVER WITH RESPECT TO THE SOFTWARE OF ANY THIRD PARTY WHICH MAY BE USED BY, INCORPORATED IN, OR SUPPLIED WITH THIS REFERENCE MANUAL, AND USER AGREES TO LOOK ONLY TO SUCH THIRD PARTY FOR ANY WARRANTY CLAIM RELATING THERETO. AUTOCHIPS INC. SHALL ALSO NOT BE RESPONSIBLE FOR ANY AUTOCHIPS DELIBERABLES MADE TO USER'S SPECIFICATION OR TO CONFORM TO A PARTICULAR STANDARD OR OPEN FORUM.

# **NutoChips**

# **Table of Contents**

| Doc   | umen    | t Revisi             | on History                                  | 2             |

|-------|---------|----------------------|---------------------------------------------|---------------|

| Lega  | al Not  | tice                 |                                             | 4             |

| Tabl  | e of (  | Contents             | 5                                           | 5             |

| List  | of Fig  | gures                |                                             | 16            |

| List  | of Ta   | bles                 |                                             | 19            |

| 1     | Intro   | oduction             | ۱                                           | 21            |

|       | 1.1     | Overview             | ,                                           | 21            |

|       | 1.2     | Module d             | escription                                  | 21            |

| 2     | Men     | ory and              | Bus Architecture                            | 22            |

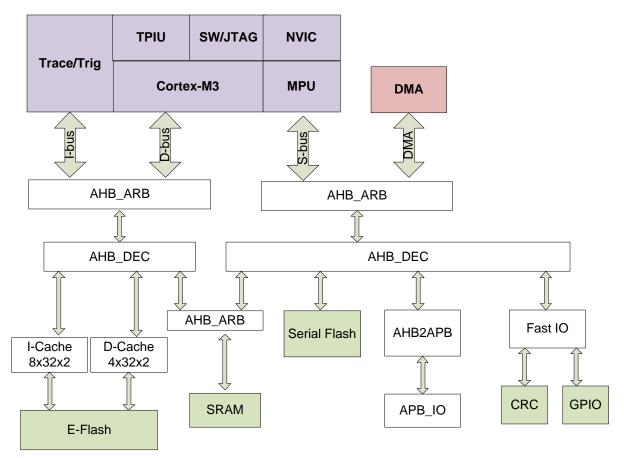

|       | 2.1     | System a             | rchitecture                                 | 22            |

|       | 2.2     | Memory of            | organization                                | 24            |

|       |         | 2.2.1                | Memory map                                  | 24            |

|       | 2.3     | Detail fun           | ction description                           | 25            |

|       |         | 2.3.1                | Internal SRAM                               | 25            |

|       |         | 2.3.2                | Bit banding                                 | 25            |

|       |         | 2.3.3                | Fast IO memory map                          | 26            |

|       |         | 2.3.4                | Internal flash memory                       | 26            |

|       |         | 2.3.5                | Read internal flash memory                  | 26            |

|       |         | 2.3.6                | Chip Model                                  | 27            |

|       |         | 2.3.7                | Chip UUID                                   | 27            |

|       |         | 2.3.8                | I-Cache and D-Cache                         | 27            |

|       |         | 2.3.9                | AHB to APB bridge                           | 27            |

|       |         | 2.3.10               | Nested Vectored Interrupt Controller (NVIC) | 27            |

|       |         | 2.3.11               | Boot configuration                          | 29            |

|       | 2.4     | Address <sup>-</sup> | Table                                       |               |

| 3     | Rese    | et                   |                                             | 32            |

|       | 3.1     | Introducti           | on                                          | 32            |

| AutoC | Chips C | onfidential          | © 2013 - 2021 AutoChips Inc.                | Page 5 of 360 |

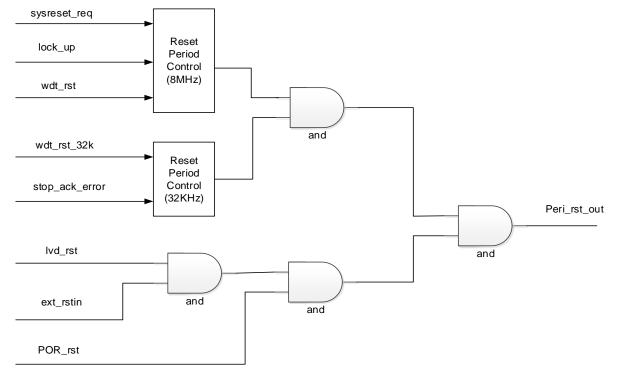

|        | 3.2                                                                                                   | Block dia                                                                                                              | igram                                                                                                                           |          |

|--------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------|

|        | 3.3                                                                                                   | Reset de                                                                                                               | tail function description                                                                                                       | 33       |

|        |                                                                                                       | 3.3.1                                                                                                                  | Power On Reset (POR)                                                                                                            | 33       |

|        |                                                                                                       | 3.3.2                                                                                                                  | System reset source                                                                                                             |          |

|        | 3.4                                                                                                   | Register                                                                                                               | mapping                                                                                                                         |          |

| 4      | Cloc                                                                                                  | : <b>k</b>                                                                                                             |                                                                                                                                 | 36       |

|        | 4.1                                                                                                   | Introduct                                                                                                              | ion                                                                                                                             |          |

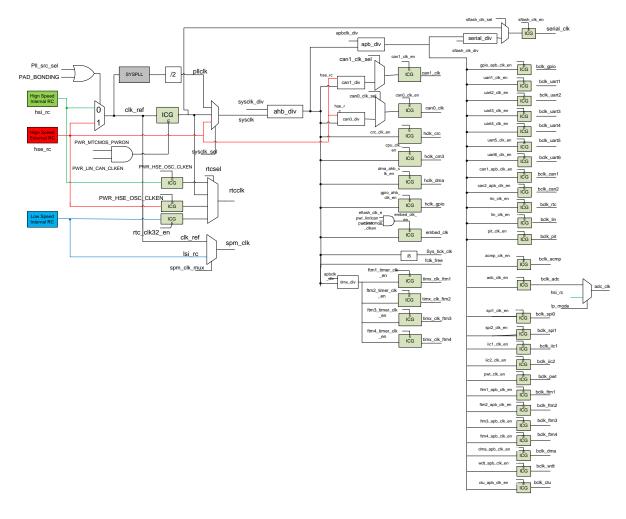

|        | 4.2                                                                                                   | Clock co                                                                                                               | ntrol diagram                                                                                                                   |          |

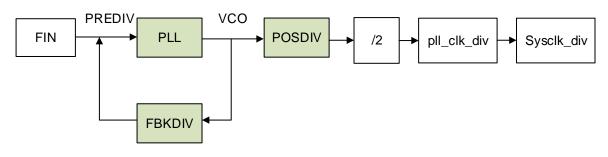

|        | 4.3                                                                                                   | System (                                                                                                               | Clock                                                                                                                           |          |

|        | 4.4                                                                                                   | Register                                                                                                               | mapping                                                                                                                         |          |

| 5      | Pow                                                                                                   | ver Mode                                                                                                               | es                                                                                                                              | 46       |

|        | 5.1                                                                                                   | Introduct                                                                                                              | ion                                                                                                                             | 46       |

|        | 5.2                                                                                                   | Power m                                                                                                                | odes                                                                                                                            | 46       |

|        | 5.3                                                                                                   | Entering                                                                                                               | and exiting power modes                                                                                                         | 46       |

|        | 5.4                                                                                                   | Module of                                                                                                              | operation in low-power modes                                                                                                    | 46       |

|        |                                                                                                       |                                                                                                                        | <b>M</b> .                                                                                                                      |          |

| 6      | Sys                                                                                                   | tem Pov                                                                                                                | ver Management                                                                                                                  | 48       |

| 6      | <b>Sys</b><br>6.1                                                                                     |                                                                                                                        | ion                                                                                                                             |          |

| 6      | -                                                                                                     | Introduct                                                                                                              | -                                                                                                                               | 48       |

| 6      | 6.1                                                                                                   | Introduct<br>Feature                                                                                                   | ion                                                                                                                             | 48<br>48 |

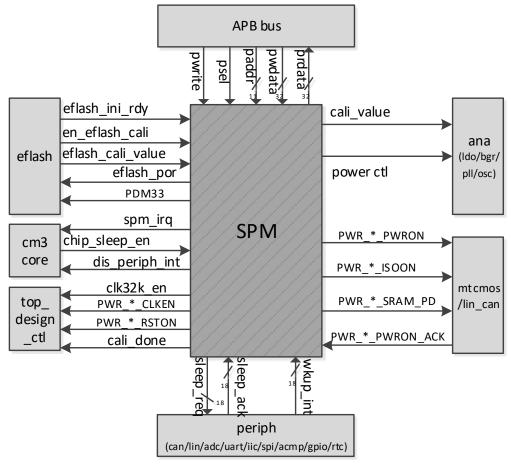

| 6      | 6.1<br>6.2                                                                                            | Introduct<br>Feature<br>Block dia                                                                                      | ion                                                                                                                             |          |

| 6      | 6.1<br>6.2<br>6.3                                                                                     | Introduct<br>Feature<br>Block dia                                                                                      | ion<br>ist                                                                                                                      |          |

| 6      | 6.1<br>6.2<br>6.3                                                                                     | Introduct<br>Feature<br>Block dia<br>Applicati                                                                         | ion<br>ist<br>Igram<br>on notes                                                                                                 |          |

| 6      | 6.1<br>6.2<br>6.3                                                                                     | Introduct<br>Feature<br>Block dia<br>Applicati<br>6.4.1<br>6.4.2                                                       | ion<br>ist<br>ogram<br>on notes<br>SPM power control program guide                                                              |          |

| 6<br>7 | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> </ul>                           | Introduct<br>Feature<br>Block dia<br>Applicati<br>6.4.1<br>6.4.2<br>Register                                           | ion<br>ist<br>or notes<br>SPM power control program guide<br>XOSC/SYSPLL power control                                          |          |

|        | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> </ul>                           | Introduct<br>Feature<br>Block dia<br>Applicati<br>6.4.1<br>6.4.2<br>Register                                           | ion<br>ist<br>on notes<br>SPM power control program guide<br>XOSC/SYSPLL power control<br>mapping                               |          |

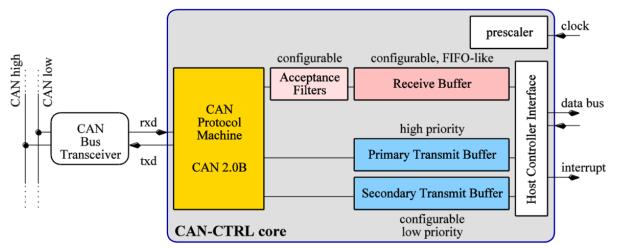

|        | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>CAN</li> </ul>              | Introduct<br>Feature<br>Block dia<br>Applicati<br>6.4.1<br>6.4.2<br>Register                                           | ion<br>ist<br>on notes<br>SPM power control program guide<br>XOSC/SYSPLL power control<br>mapping                               |          |

|        | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>CAN</li> </ul>              | Introduct<br>Feature<br>Block dia<br>Applicati<br>6.4.1<br>6.4.2<br>Register                                           | ionist<br>Igram<br>on notes<br>SPM power control program guide<br>XOSC/SYSPLL power control<br>mapping<br>ion                   |          |

|        | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>CAN</li> </ul>              | Introduct<br>Feature<br>Block dia<br>Applicati<br>6.4.1<br>6.4.2<br>Register<br>Introduct<br>7.1.1<br>7.1.2            | ion<br>ist<br>agram<br>on notes<br>SPM power control program guide<br>XOSC/SYSPLL power control<br>mapping<br>The CAN-CTRL core |          |

|        | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>CAN</li> <li>7.1</li> </ul> | Introduct<br>Feature<br>Block dia<br>Applicati<br>6.4.1<br>6.4.2<br>Register<br>Introduct<br>7.1.1<br>7.1.2<br>Feature | ionist<br>agram                                                                                                                 |          |

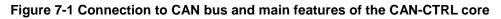

|     | 7.3.1     | Message buffers concept          | 59  |

|-----|-----------|----------------------------------|-----|

|     | 7.3.2     | Receive buffer                   | .60 |

|     | 7.3.3     | Transmit buffer                  | .60 |

| 7.4 | Register  | definition                       | .61 |

| 7.5 | General   | operation                        | 73  |

|     | 7.5.1     | The bus off state                | 73  |

|     | 7.5.2     | Acceptance filters               | 73  |

|     | 7.5.3     | Message reception                | .74 |

|     | 7.5.4     | Handling message receptions      | .74 |

|     | 7.5.5     | Message transmission             | 75  |

|     | 7.5.6     | Message transmission abort       | 76  |

|     | 7.5.7     | A full STB                       | .77 |

|     | 7.5.8     | Extended status and error report | 77  |

|     | 7.5.9     | Extended features                | .78 |

|     | 7.5.10    | Software reset                   | .80 |

|     | 7.5.1     | CAN bit time                     | .83 |

| LIN |           |                                  | 86  |

| 8.1 | Introduc  | tion                             | 86  |

| 8.2 | Feature   | list                             | .86 |

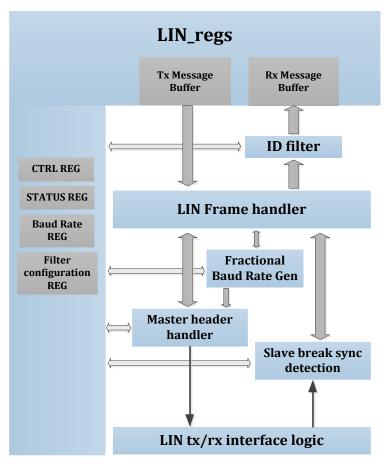

| 8.3 | Block dia | agram                            | .86 |

| 8.4 | Applicati | ion note                         | .87 |

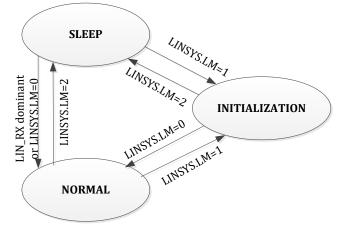

|     | 8.4.1     | Operating modes                  | .87 |

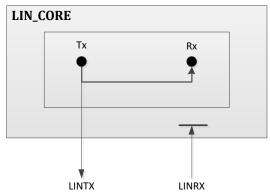

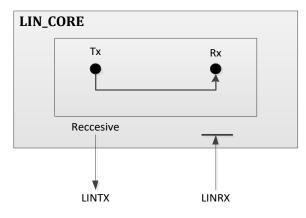

|     | 8.4.2     | Test modes                       | .88 |

|     | 8.4.3     | Baud rate generation             | .89 |

|     | 8.4.4     | Error detection                  | .89 |

|     | 8.4.5     | Interrupt table                  | .90 |

|     | 8.4.6     | Master mode                      | .90 |

|     | 8.4.7     | Slave mode                       | .91 |

|     | 8.4.8     | Register definition              | .92 |

8

# **VutoChips**

| 9  | UAR   | т          |                             |     |

|----|-------|------------|-----------------------------|-----|

|    | 9.1   | Introduct  | ion                         |     |

|    | 9.2   | Features   |                             |     |

|    | 9.3   | Block dia  | ıgram                       |     |

|    | 9.4   | Input & C  | Dutput timing               |     |

|    | 9.5   | Basic UA   | ART functions               |     |

|    |       | 9.5.1      | Noise detection             |     |

|    |       | 9.5.2      | Baud rate description       |     |

|    | 9.6   | Hardwar    | e flow control function     |     |

|    | 9.7   | RS485 fu   | Inction                     |     |

|    | 9.8   | LIN funct  | ion                         |     |

|    | 9.9   | Two chip   | power mode                  |     |

|    | 9.10  | Baud rate  | e configuration description | 110 |

|    | 9.11  | Configure  | e note                      | 111 |

|    | 9.12  | Register   | Definition                  | 112 |

| 10 | ADC   |            |                             | 122 |

|    | 10.1  | ADC intro  | oduction                    |     |

|    | 10.2  | ADC feat   | tures                       |     |

|    | 10.3  | ADC fund   | ctional description         |     |

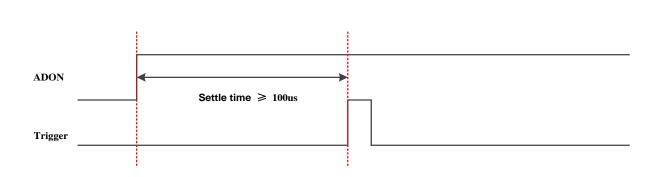

|    |       | 10.3.1     | ADC power on sequence       |     |

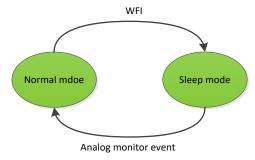

|    |       | 10.3.2     | ADC power modes             |     |

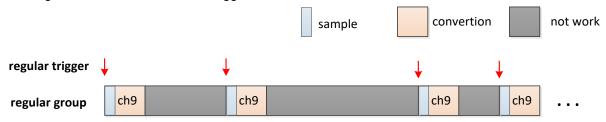

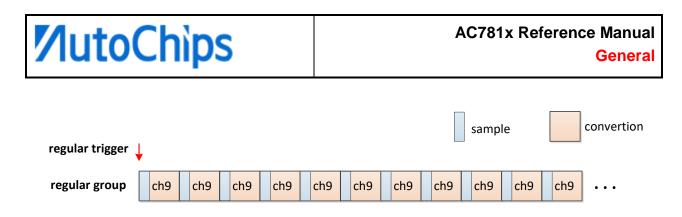

|    |       | 10.3.3     | ADC operation modes         |     |

|    | 10.4  | Analog m   | nonitor                     |     |

|    | 10.5  | Status fla | ag description              |     |

|    | 10.6  | Calibratio | on                          |     |

|    | 10.7  | Sampling   | g conversion time           |     |

|    | 10.8  | Tempera    | ture sensor                 | 134 |

|    | 10.9  | DMA acc    | cess                        | 134 |

|    | 10.10 | ) Program  | guide                       |     |

© 2013 - 2021 AutoChips Inc.

Page 8 of 360

|    |       | 10.10.1    | Normal power mode             | 135 |

|----|-------|------------|-------------------------------|-----|

|    |       | 10.10.2    | Low power mode                | 135 |

|    | 10.11 | ADC regi   | ister definition              | 135 |

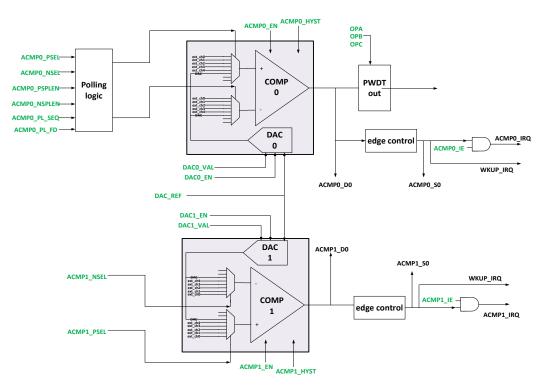

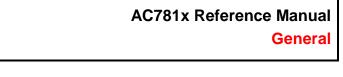

| 11 | ACM   | IP         |                               | 142 |

|    | 11.1  | Introduct  | ion                           | 142 |

|    | 11.2  | Features   |                               | 142 |

|    |       | 11.2.1     | Block diagram                 | 142 |

|    | 11.3  | Functiona  | al description                | 143 |

|    |       | 11.3.1     | ACMP0                         | 143 |

|    |       | 11.3.2     | ACMP1                         | 144 |

|    |       | 11.3.3     | Low power wakeup              | 144 |

|    | 11.4  | Memory     | map and register definition   | 144 |

|    | 11.5  | Interrupts | 5                             | 153 |

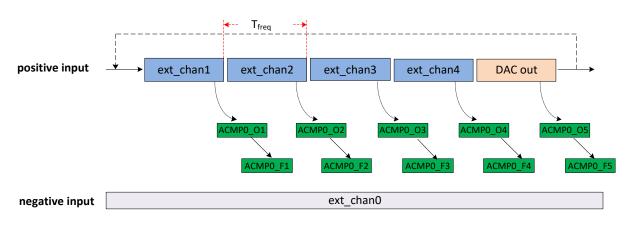

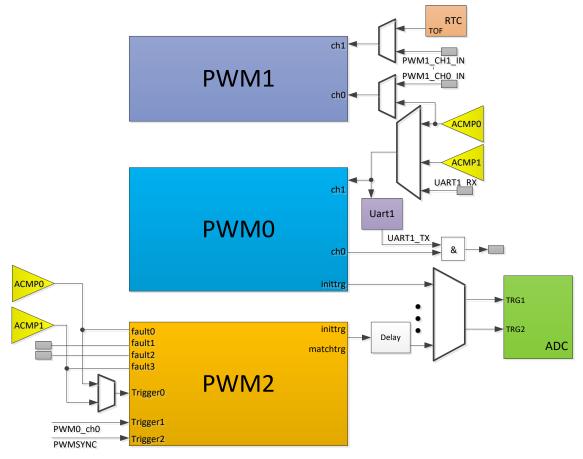

| 12 | PWN   | 1          |                               | 154 |

|    | 12.1  | Introduct  | ion                           | 154 |

|    |       | 12.1.1     | PWM features                  |     |

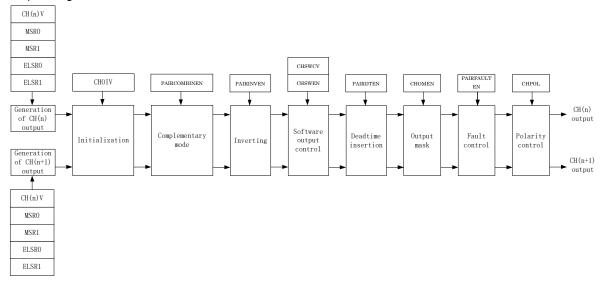

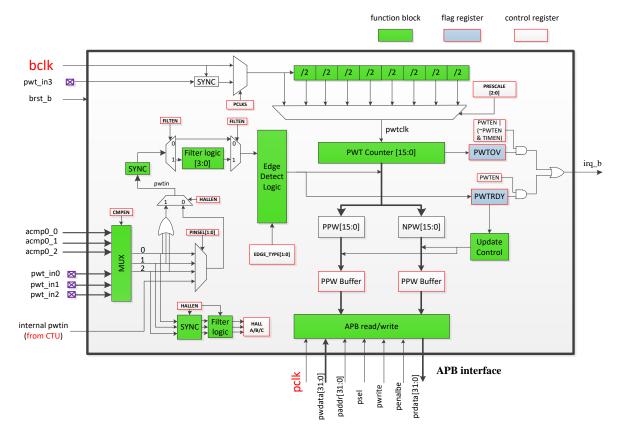

|    |       | 12.1.2     | Block diagram                 |     |

|    | 12.2  | Memory     | map and register definition   |     |

|    | 12.3  | Functiona  | al description                |     |

|    |       | 12.3.1     | Clock source                  |     |

|    |       | 12.3.2     | Prescaler                     |     |

|    |       | 12.3.3     | Counter                       |     |

|    |       | 12.3.4     | Operation mode                |     |

|    |       | 12.3.5     | Input capture mode            |     |

|    |       | 12.3.6     | Output Compare mode           |     |

|    |       | 12.3.7     | Edge-Aligned PWM(EPWM) mode   |     |

|    |       | 12.3.8     | Center-Aligned PWM(CPWM) mode |     |

|    |       | 12.3.9     | Combine mode                  |     |

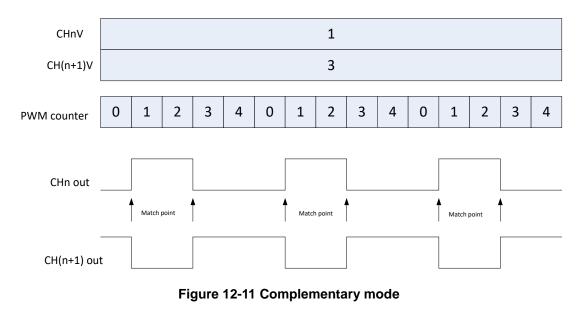

|    |       | 12.3.10    | Complementary mode            |     |

|    |       |            |                               |     |

Page 9 of 360

|    |      | 12.3.11    | Registers updated from write buffers           |     |

|----|------|------------|------------------------------------------------|-----|

|    |      | 12.3.12    | PWM synchronization                            | 190 |

|    |      | 12.3.13    | Inverting                                      | 190 |

|    |      | 12.3.14    | Channel trigger output                         | 191 |

|    |      | 12.3.15    | Initialization trigger                         | 191 |

|    |      | 12.3.16    | Capture Test mode                              | 191 |

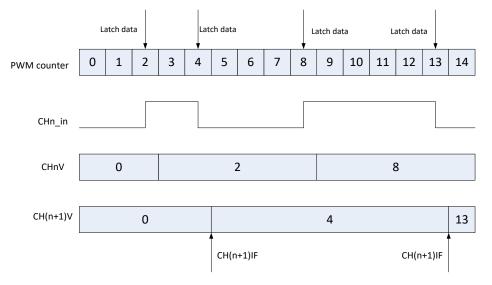

|    |      | 12.3.17    | Dual Edge Capture mode                         | 191 |

|    |      | 12.3.18    | Software output control                        | 192 |

|    |      | 12.3.19    | Deadtime insertion                             | 193 |

|    |      | 12.3.20    | Fault control                                  |     |

|    |      | 12.3.21    | Polarity control                               | 194 |

|    |      | 12.3.22    | Features priority                              | 194 |

|    | 12.4 | PWM inte   | errupts                                        | 195 |

|    |      | 12.4.1     | Count Overflow interrupt                       | 195 |

|    |      | 12.4.2     | Channel interrupt                              | 195 |

|    |      | 12.4.3     | Fault interrupt                                | 195 |

| 13 | Puls | e Width    | Detect Timer(PWDT)                             | 196 |

|    | 13.1 | Introducti | ion                                            | 196 |

|    | 13.2 | Features   |                                                | 196 |

|    | 13.3 | Functiona  | al description                                 | 196 |

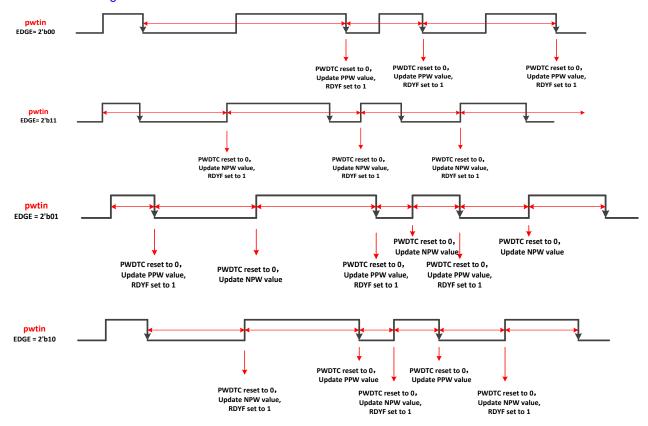

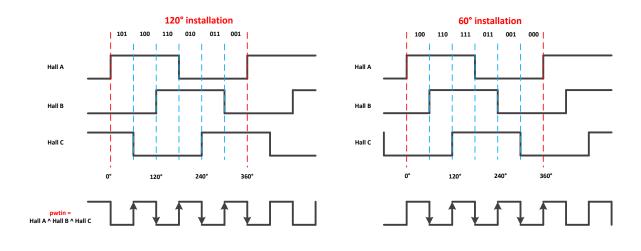

|    |      | 13.3.1     | Pulse Width Measurement function               | 197 |

|    |      | 13.3.2     | Timer function                                 | 200 |

|    |      | 13.3.3     | Reset operation                                | 201 |

|    | 13.4 | Program    | guide                                          | 201 |

|    |      | 13.4.1     | Pulse Width Measurement function program guide | 201 |

|    |      | 13.4.2     | Timer function program guide                   | 201 |

|    | 13.5 | Register   | definition                                     | 202 |

|    |      |            |                                                |     |

| 14 | ТІМ  | ER         |                                                | 205 |

| 14 |      |            | ion                                            |     |

|    | 14.2 | Features   |                                       | )5 |

|----|------|------------|---------------------------------------|----|

|    | 14.3 | Functiona  | al description                        | )5 |

|    |      | 14.3.1     | General operation20                   | )6 |

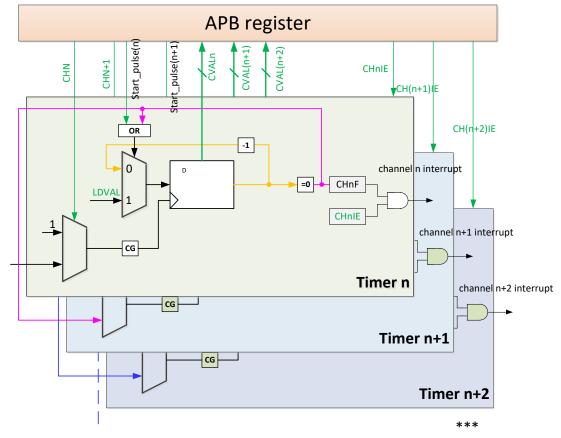

|    |      | 14.3.2     | Chained timers                        | )6 |

|    | 14.4 | Memory     | map and register definition20         | )6 |

|    | 14.5 | Interrupts |                                       | )9 |

| 15 | сти  |            | 21                                    | 0  |

|    | 15.1 | Introduct  | on21                                  | 0  |

|    | 15.2 | Features   |                                       | 0  |

|    | 15.3 | Function   | description21                         | 0  |

|    |      | 15.3.1     | ACMP output capture                   | 1  |

|    |      | 15.3.2     | ADC hardware trigger21                | 1  |

|    | 15.4 | Register   | definition21                          | 1  |

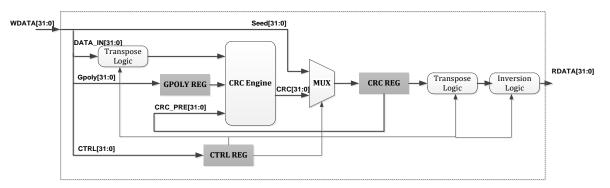

| 16 | CRC  |            | 21                                    | 5  |

|    | 16.1 | Introduct  | on21                                  | 5  |

|    | 16.2 | Features   |                                       | 5  |

|    | 16.3 | Block dia  | gram21                                | 5  |

|    | 16.4 | Memory     | map and register descriptions21       | 5  |

|    | 16.5 | Functiona  | al description21                      | 8  |

|    |      | 16.5.1     | CRC initialization/reinitialization21 | 8  |

|    |      | 16.5.2     | CRC calculations                      | 8  |

|    |      | 16.5.3     | Transpose feature21                   | 8  |

|    |      | 16.5.4     | Types of transpose                    | 8  |

|    |      | 16.5.5     | CRC result complement                 | 20 |

|    |      | 16.5.6     | CRC data register (CRC_DATA)22        | 20 |

|    |      | 16.5.7     | CRC Polynomial register (CRC_GPOLY)22 | 20 |

|    |      | 16.5.8     | CRC Control register (CRC_CTRL)22     | 20 |

|    | 16.6 | Program    | guide22                               | 20 |

|    |      | 16.6.1     | 16-bit CRC22                          | 20 |

Page 11 of 360

|    |      | 16.6.2      | 32-bit CRC                    | 221 |

|----|------|-------------|-------------------------------|-----|

| 17 | GPI  | 0           |                               | 222 |

|    | 17.1 | Introduct   | ion                           | 222 |

|    | 17.2 | Features    | S                             |     |

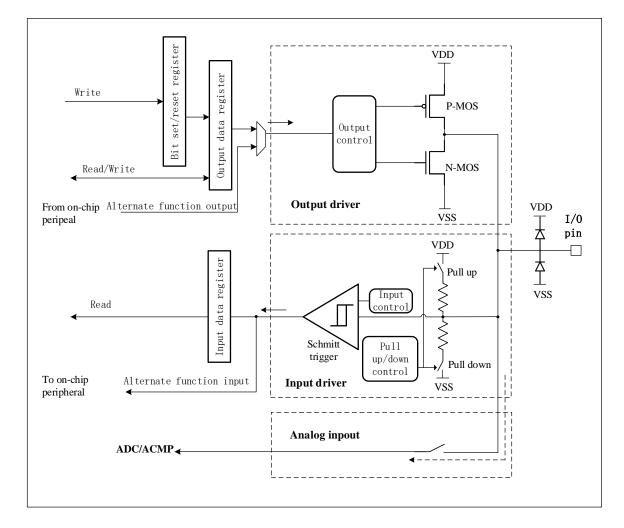

|    | 17.3 | Block dia   | agram                         | 223 |

|    | 17.4 | Mode of     | operation                     | 223 |

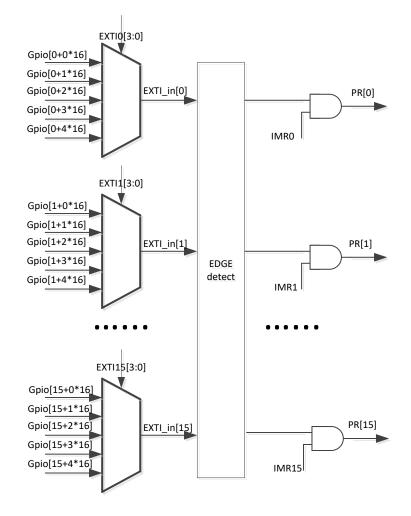

|    |      | 17.4.1      | External interrupt            | 223 |

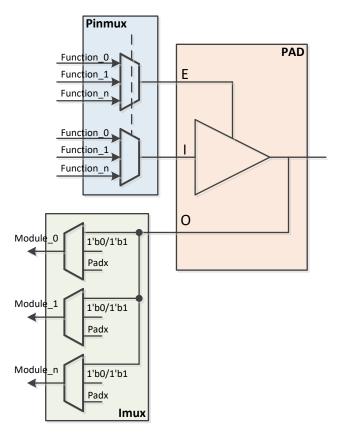

|    |      | 17.4.2      | Multi-Function                | 225 |

|    | 17.5 | Application | on note                       | 228 |

|    |      | 17.5.1      | External interrupt            |     |

|    |      | 17.5.2      | Multi-Function                | 228 |

|    |      | 17.5.3      | GPIO function                 | 228 |

|    |      | 17.5.4      | Programming guide             | 228 |

|    | 17.6 | Memory      | map and register descriptions | 229 |

| 18 | 12C. |             |                               | 238 |

|    | 18.1 | Introduct   | ion                           | 238 |

|    | 18.2 | Features    | 5                             | 238 |

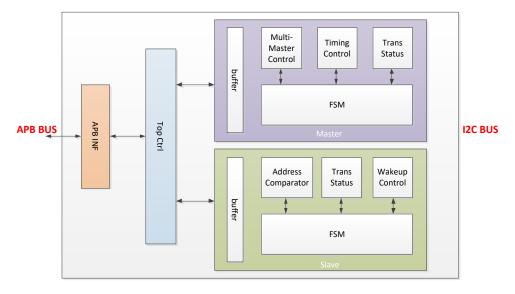

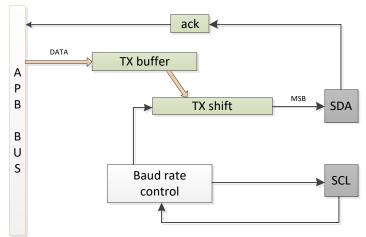

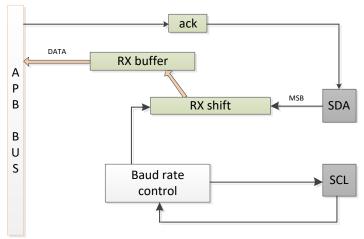

|    | 18.3 | Block dia   | agram                         | 238 |

|    | 18.4 | Mode of     | operation                     |     |

|    | 18.5 | Memory      | map and register descriptions | 239 |

|    | 18.6 | Function    | al description                | 248 |

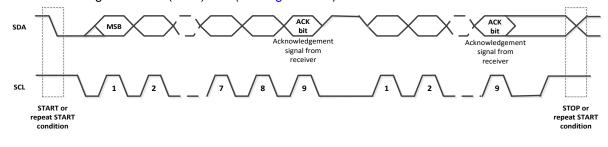

|    |      | 18.6.1      | Data flow & Algorithm         | 248 |

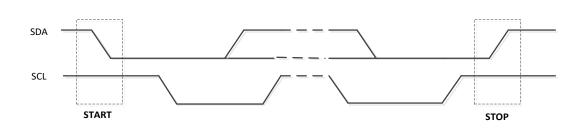

|    |      | 18.6.2      | Input & Output timing         | 248 |

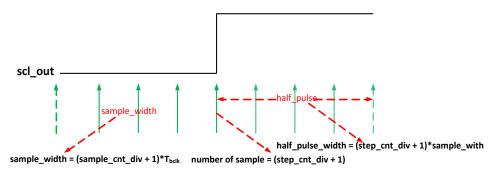

|    |      | 18.6.3      | Master SCL output timing set  | 249 |

|    |      | 18.6.4      | Data transmission             | 249 |

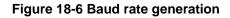

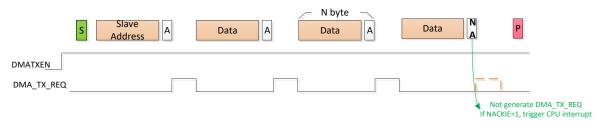

|    |      | 18.6.5      | DMA operation                 |     |

|    |      | 18.6.6      | Slave low power wakeup        |     |

|    |      | 18.6.7      | Interrupt                     |     |

|    | 18.7 | Program     | guide                         |     |

Page 12 of 360

|    |       | 18.7.1     | Description              | 253 |

|----|-------|------------|--------------------------|-----|

|    |       | 18.7.2     | Master transmitter       | 253 |

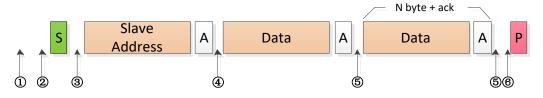

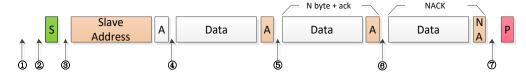

|    |       | 18.7.3     | Master receiver          | 254 |

|    |       | 18.7.4     | Master combined format   | 254 |

|    |       | 18.7.5     | Slave                    | 255 |

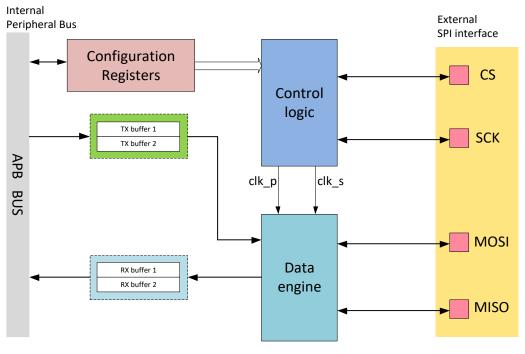

| 19 | SPI   |            |                          | 256 |

|    | 19.1  | Introduct  | tion                     | 256 |

|    | 19.2  | Feature I  | list                     | 256 |

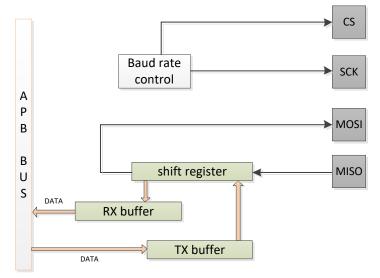

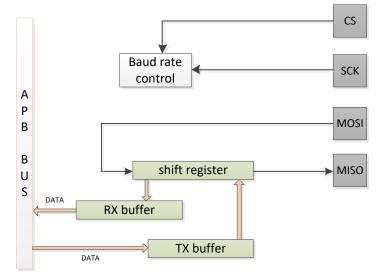

|    | 19.3  | Block dia  | agram                    | 257 |

|    | 19.4  | Data flow  | w & Algorithm            | 257 |

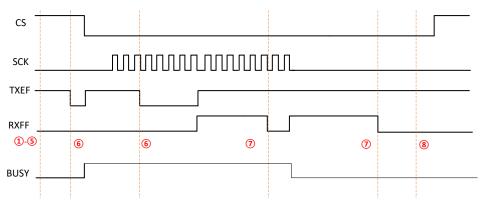

|    | 19.5  | Input & C  | Output timing            | 258 |

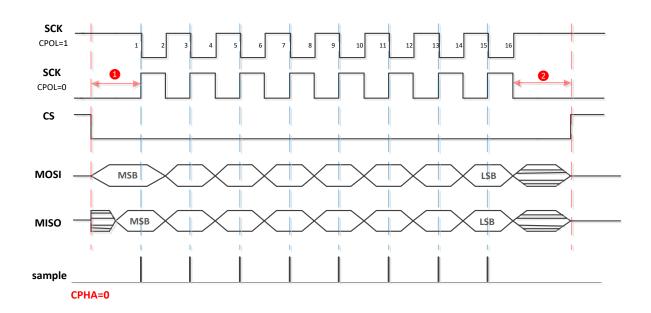

|    |       | 19.5.1     | CPHA = 0 transfer format | 258 |

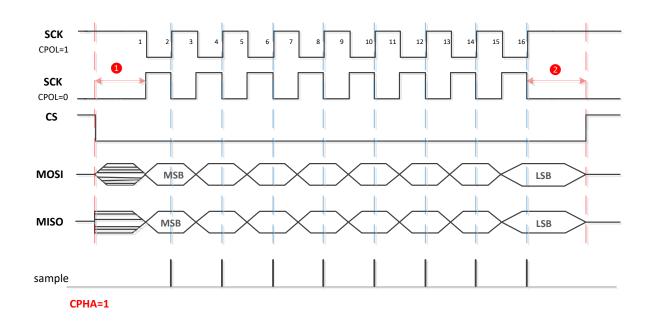

|    |       | 19.5.2     | CPHA = 1 transfer format | 259 |

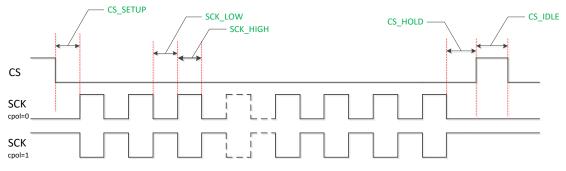

|    | 19.6  | Master S   | SCK output timing set    | 260 |

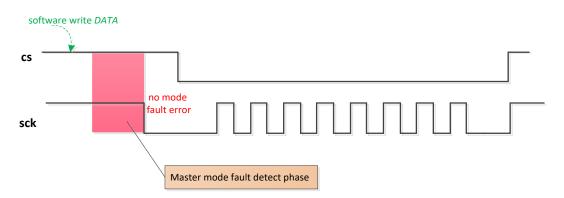

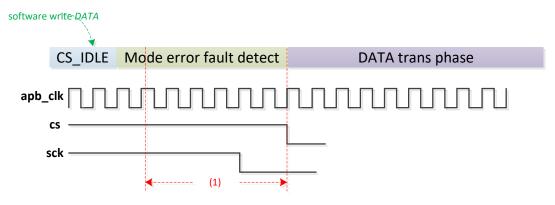

|    | 19.7  | Master m   | node fault detect        | 260 |

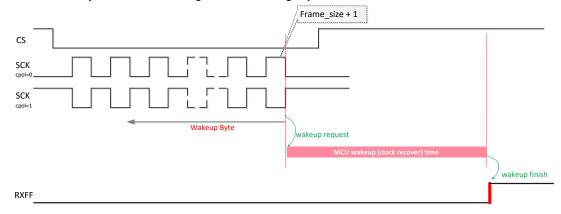

|    | 19.8  | Slave lov  | w power wakeup           | 261 |

|    | 19.9  | Interrupt  | t                        | 262 |

|    | 19.10 | ) Master C | CS continuous mode       | 262 |

|    | 19.11 | Master C   | CS discontinuous output  |     |

|    | 19.12 | 2 Slave mo | ode                      |     |

|    | 19.13 | 3 DMA mo   | ode                      |     |

|    | 19.14 | Register   | definition               |     |

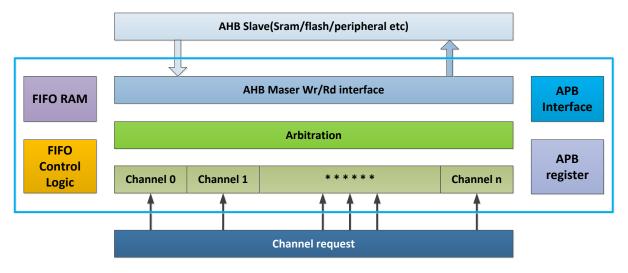

| 20 | DMA   | ۱          |                          | 269 |

|    | 20.1  | Introduct  | tion                     | 269 |

|    | 20.2  | Features   | 3                        | 269 |

|    | 20.3  | Block dia  | agram                    | 270 |

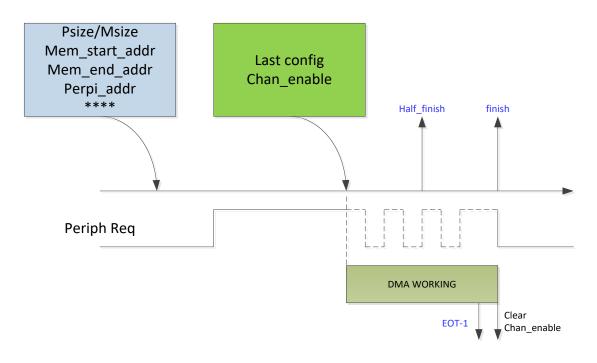

|    | 20.4  | Mode of    | operations               | 270 |

|    | 20.5  | Function   | n description            | 270 |

|    |       | 20.5.1     | DMA request mapping      | 270 |

Page 13 of 360

|    |                              | 20.5.2                                                                                                   | DMA arbiter                                                                                                                                                                                       | 270               |

|----|------------------------------|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

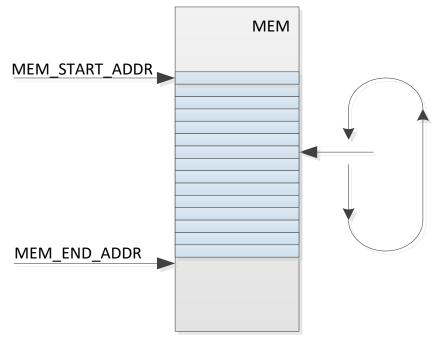

|    |                              | 20.5.3                                                                                                   | Configuration guide                                                                                                                                                                               | 271               |

|    | 20.6                         | Memory                                                                                                   | map and register descriptions                                                                                                                                                                     | 273               |

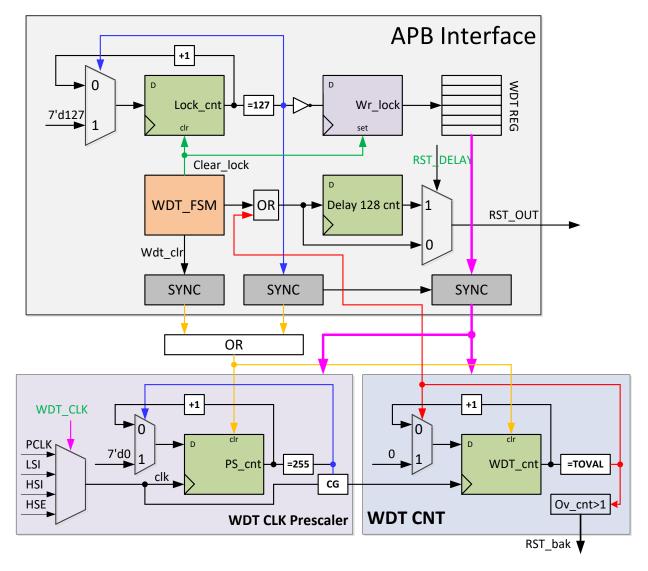

| 21 | WD                           | г                                                                                                        |                                                                                                                                                                                                   |                   |

|    | 21.1                         | Introduct                                                                                                | ion                                                                                                                                                                                               |                   |

|    | 21.2                         | Features                                                                                                 |                                                                                                                                                                                                   |                   |

|    | 21.3                         | Block dia                                                                                                | agram                                                                                                                                                                                             |                   |

|    | 21.4                         | Mode of                                                                                                  | operation                                                                                                                                                                                         |                   |

|    | 21.5                         | Memory                                                                                                   | map and register descriptions                                                                                                                                                                     |                   |

|    | 21.6                         | Function                                                                                                 | al description                                                                                                                                                                                    |                   |

|    |                              | 21.6.1                                                                                                   | Watchdog refresh mechanism                                                                                                                                                                        |                   |

|    |                              | 21.6.2                                                                                                   | Configuring the Watchdog                                                                                                                                                                          |                   |

|    |                              | 21.6.3                                                                                                   | Using interrupts to delay watchdog reset                                                                                                                                                          |                   |

|    |                              | 21.6.4                                                                                                   | Backup reset                                                                                                                                                                                      |                   |

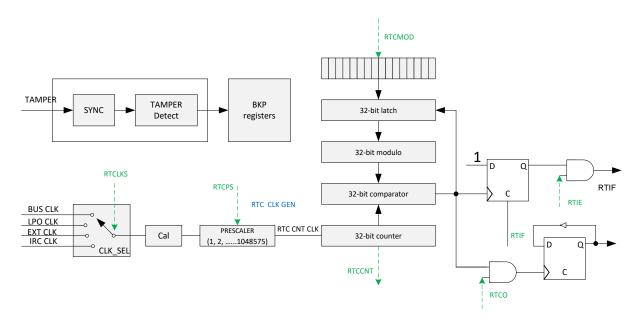

| 22 | RTC                          |                                                                                                          |                                                                                                                                                                                                   |                   |

|    | 22.1                         | Introduct                                                                                                | ion                                                                                                                                                                                               |                   |

|    | ~~~~                         | _                                                                                                        |                                                                                                                                                                                                   | 200               |

|    | 22.2                         | Features                                                                                                 |                                                                                                                                                                                                   |                   |

|    | 22.2<br>22.3                 |                                                                                                          | agram                                                                                                                                                                                             |                   |

|    | 22.3                         | Block dia                                                                                                | agramoperation                                                                                                                                                                                    | 290               |

|    | 22.3<br>22.4                 | Block dia<br>Mode of                                                                                     | -                                                                                                                                                                                                 | 290               |

|    | 22.3<br>22.4<br>22.5         | Block dia<br>Mode of<br>Memory                                                                           | operation                                                                                                                                                                                         | 290<br>290<br>290 |

|    | 22.3<br>22.4<br>22.5         | Block dia<br>Mode of<br>Memory                                                                           | operation<br>map and register descriptions                                                                                                                                                        |                   |

|    | 22.3<br>22.4<br>22.5         | Block dia<br>Mode of<br>Memory<br>Function                                                               | operation<br>map and register descriptionsal description                                                                                                                                          |                   |

|    | 22.3<br>22.4<br>22.5         | Block dia<br>Mode of<br>Memory<br>Function<br>22.6.1                                                     | operation<br>map and register descriptions<br>al description<br>Low power mode operation                                                                                                          |                   |

| 23 | 22.3<br>22.4<br>22.5<br>22.6 | Block dia<br>Mode of<br>Memory<br>Function<br>22.6.1<br>22.6.2<br>22.6.3                                 | operation<br>map and register descriptions<br>al description<br>Low power mode operation<br>RTC backup registers                                                                                  |                   |

| 23 | 22.3<br>22.4<br>22.5<br>22.6 | Block dia<br>Mode of<br>Memory<br>Function<br>22.6.1<br>22.6.2<br>22.6.3<br>edded F                      | operation<br>map and register descriptions<br>al description<br>Low power mode operation<br>RTC backup registers<br>Configuration sequence                                                        |                   |

| 23 | 22.3<br>22.4<br>22.5<br>22.6 | Block dia<br>Mode of<br>Memory<br>Function<br>22.6.1<br>22.6.2<br>22.6.3<br>edded F                      | operation<br>map and register descriptions<br>al description<br>Low power mode operation<br>RTC backup registers<br>Configuration sequence                                                        |                   |

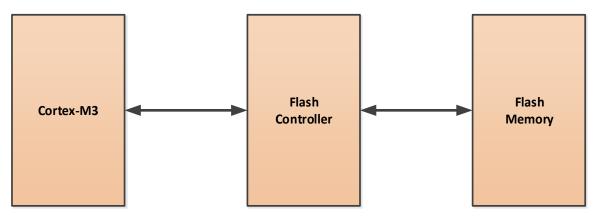

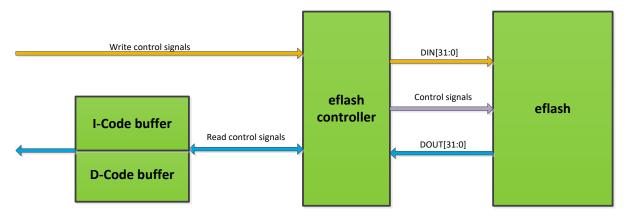

| 23 | 22.3<br>22.4<br>22.5<br>22.6 | Block dia<br>Mode of<br>Memory<br>Function<br>22.6.1<br>22.6.2<br>22.6.3<br>edded F<br>Embedde           | operation<br>map and register descriptions<br>al description<br>Low power mode operation<br>RTC backup registers<br>Configuration sequence<br>Flash<br>ed flash function overview                 |                   |

| 23 | 22.3<br>22.4<br>22.5<br>22.6 | Block dia<br>Mode of<br>Memory<br>Function<br>22.6.1<br>22.6.2<br>22.6.3<br>edded F<br>Embedde<br>23.1.1 | operation<br>map and register descriptions<br>al description<br>Low power mode operation<br>RTC backup registers<br>Configuration sequence<br>Flash<br>ed flash function overview<br>Introduction |                   |

Page 14 of 360

|    |      | 23.1.4      | Data flow & Algorithm                | 298 |

|----|------|-------------|--------------------------------------|-----|

|    | 23.2 | Embedde     | ed flash memory organization         | 298 |

|    | 23.3 | Embedde     | ed flash protect                     | 299 |

|    |      | 23.3.1      | Read and write protection            | 299 |

|    |      | 23.3.2      | Others                               |     |

|    | 23.4 | Program     | guide                                |     |

|    |      | 23.4.1      | Brief introduction                   |     |

|    |      | 23.4.2      | Command operation description        |     |

|    | 23.5 | Register    | definition                           |     |

| 24 | Seri | al Flash    |                                      | 316 |

|    | 24.1 | Serial FL   | ASH function overview                | 316 |

|    |      | 24.1.1      | Introduction                         | 316 |

|    |      | 24.1.2      | Feature list:                        | 316 |

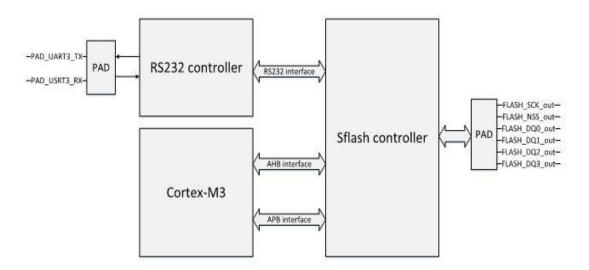

|    |      | 24.1.3      | Block diagram                        | 316 |

|    | 24.2 | Application | on note                              | 316 |

|    |      | 24.2.1      | Clock setting                        | 316 |

|    |      | 24.2.2      | RISC access NOR flash                | 317 |

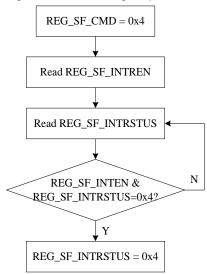

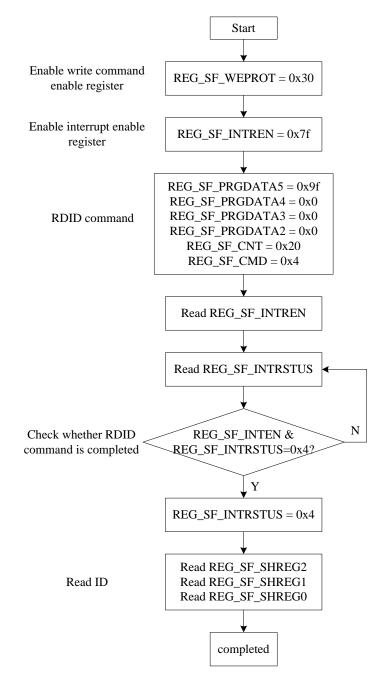

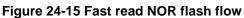

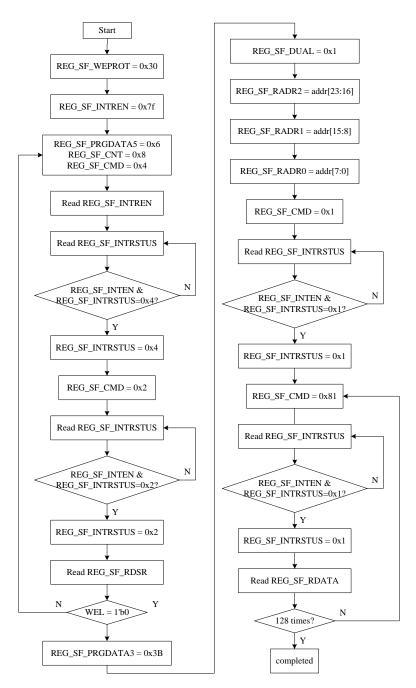

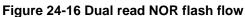

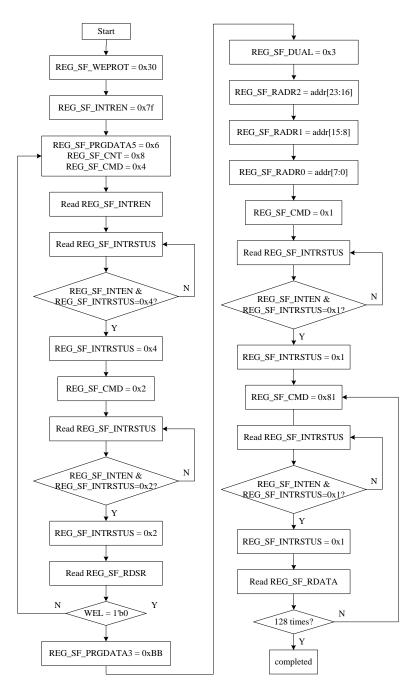

|    |      | 24.2.3      | Read NOR flash id                    | 317 |

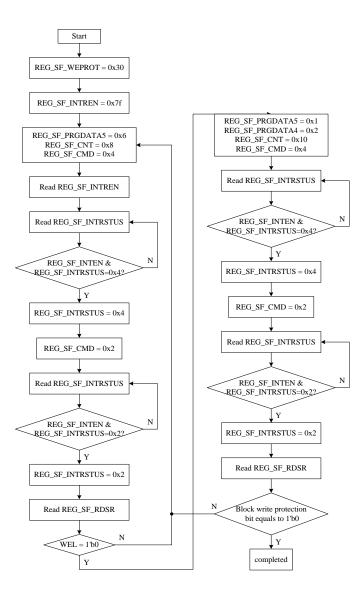

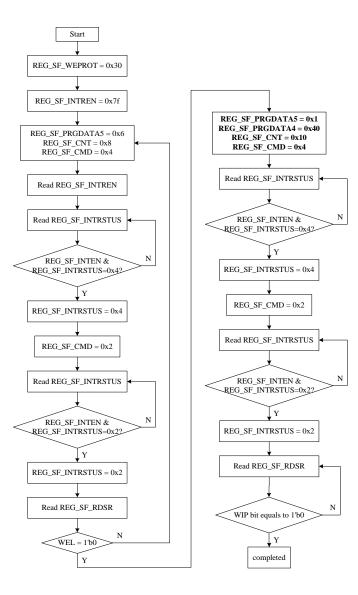

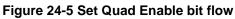

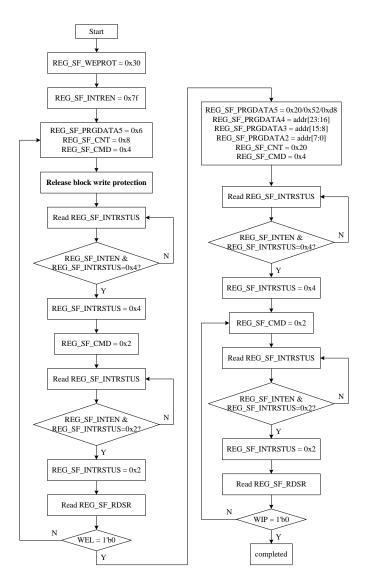

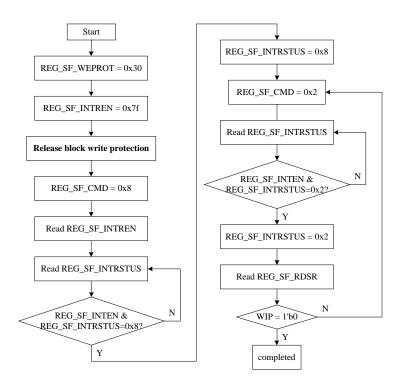

|    |      | 24.2.4      | Write status register (WRSR)         | 319 |

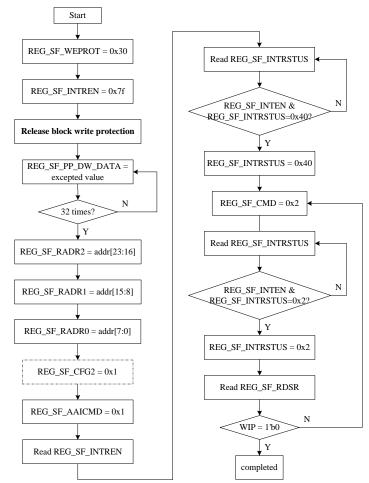

|    |      | 24.2.5      | Erase NOR flash (sector/block erase) |     |

|    |      | 24.2.6      | Erase NOR flash (chip erase)         |     |

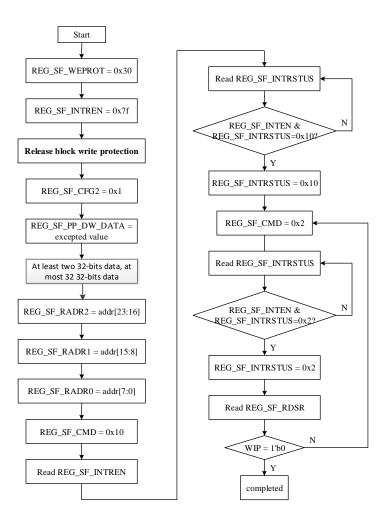

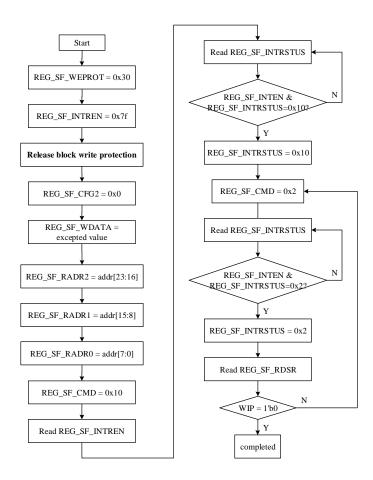

|    |      | 24.2.7      | Page Program NOR flash               |     |

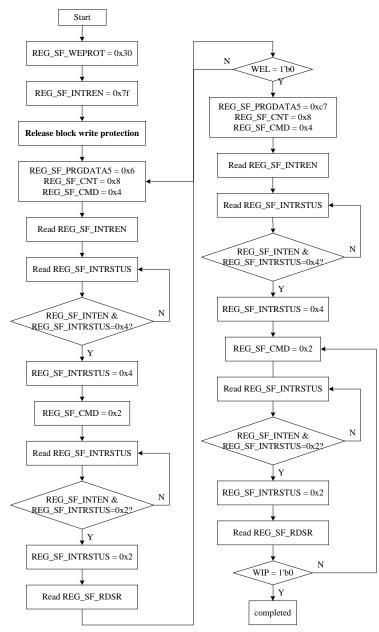

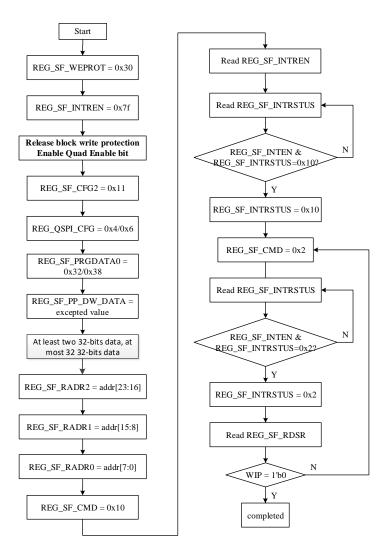

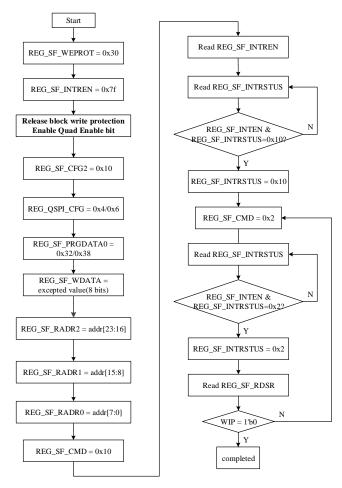

|    |      | 24.2.8      | 4 x I/O Page Program(4PP)            |     |

|    |      | 24.2.9      | AAI program NOR flash                |     |

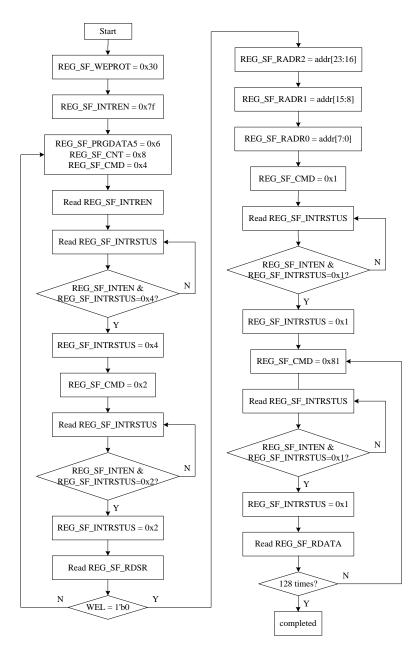

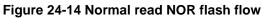

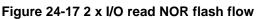

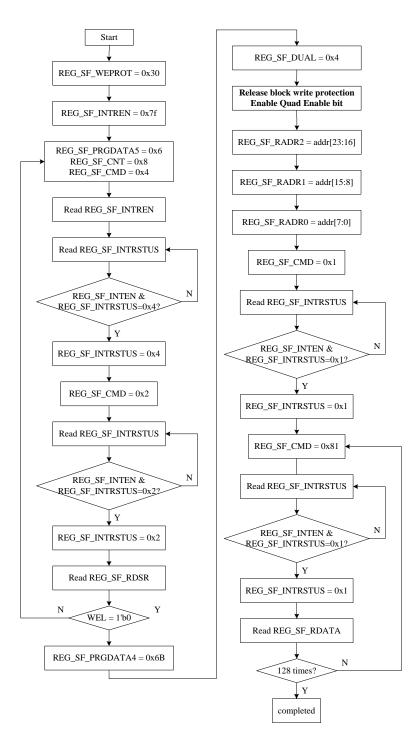

|    |      | 24.2.10     | Read NOR flash                       |     |

|    | 24.3 | System b    | boot from serial flash               |     |

|    | 24.4 | Register    | definitions                          |     |

# **//utoChips**

# **List of Figures**

| Figure 2-1 System architecture                                                 |                |

|--------------------------------------------------------------------------------|----------------|

| Figure 3-1 Reset block diagram                                                 |                |

| Figure 4-1 Clock control diagram                                               |                |

| Figure 4-2 System clock diagram                                                |                |

| Figure 6-1 SPM block diagram                                                   |                |

| Figure 7-1 Connection to CAN bus and main features of the CAN-CTRL core        |                |

| Figure 7-2 Message buffers concept                                             |                |

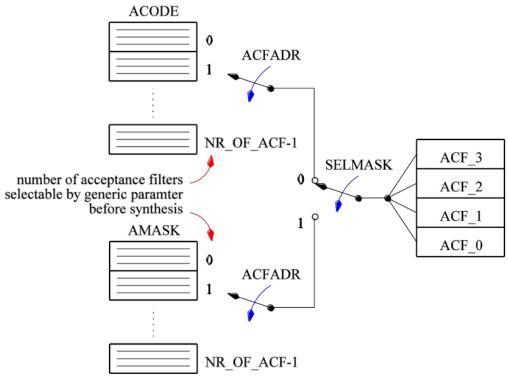

| Figure 7-3 Access to the acceptance filters                                    |                |

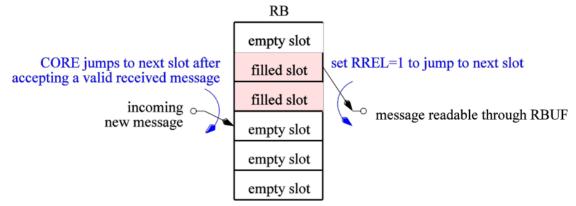

| Figure 7-4 Schematic of the FIFO-like RB (example with 6 slots)                | 74             |

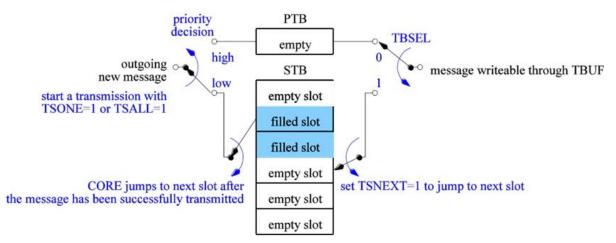

| Figure 7-5 Schematic of PTB and STB in FIFO mode (empty PTB and 6 STB slots)   | 75             |

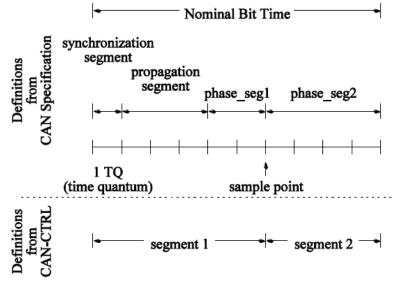

| Figure 7-6 CAN Bit Timing Specifications                                       |                |

| Figure 8-1 LINCORE block diagram                                               |                |

| Figure 8-2 LINCORE operating modes                                             |                |

| Figure 8-3 Loop back mode                                                      |                |

| Figure 8-4 Self-test mode                                                      |                |

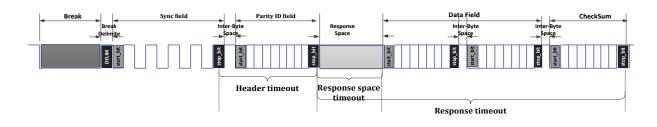

| Figure 8-5 The structure of a frame                                            |                |

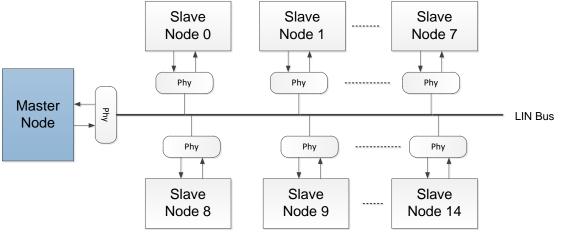

| Figure 8-6 LIN bus structure                                                   |                |

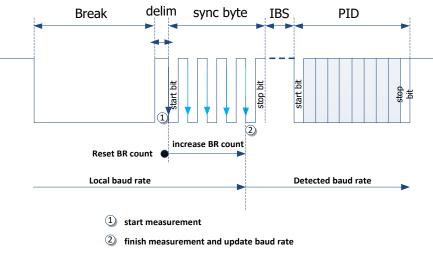

| Figure 8-7 LIN header reception                                                |                |

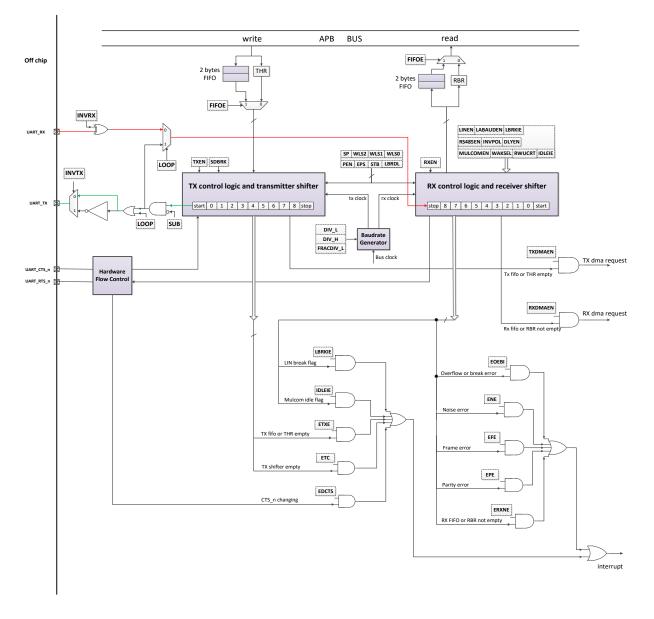

| Figure 9-1 UART block diagram                                                  |                |

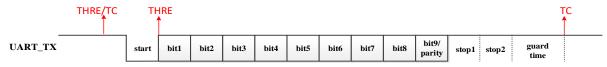

| Figure 9-2 UART transmitter flow                                               |                |

| Figure 9-2 UART receiver flow                                                  |                |

|                                                                                |                |

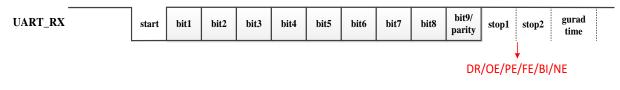

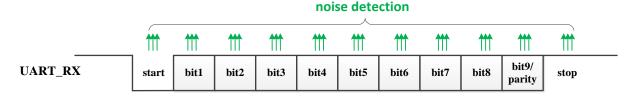

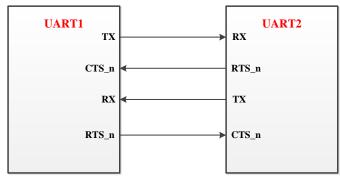

| Figure 9-4 UART noise detection<br>Figure 9-5 Hardware flow control connection |                |

|                                                                                |                |

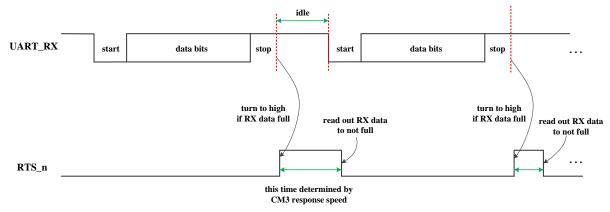

| Figure 9-6 Hardware flow control principle                                     |                |

| Figure 9-7 Single byte data transmission                                       |                |

| Figure 9-8 Multiple bytes data transmission                                    |                |

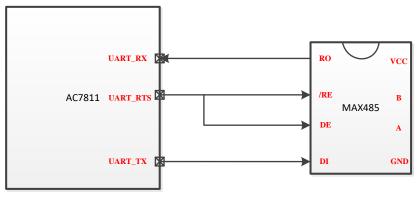

| Figure 9-9 Practical circuit connection                                        |                |

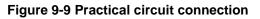

| Figure 9-10 LIN frame flow                                                     |                |

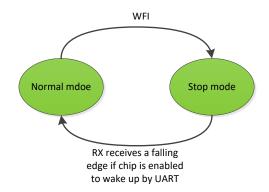

| Figure 9-11 Chip normal mode and stop mode condition                           |                |

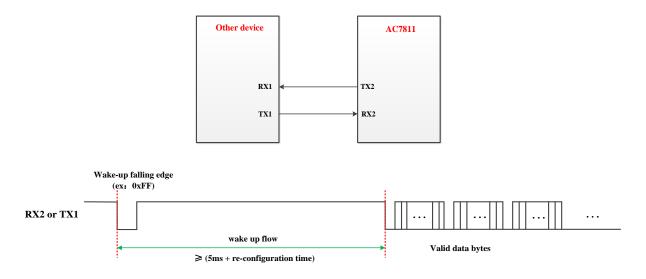

| Figure 9-12 Typical flow for waking up the chip by UART                        |                |

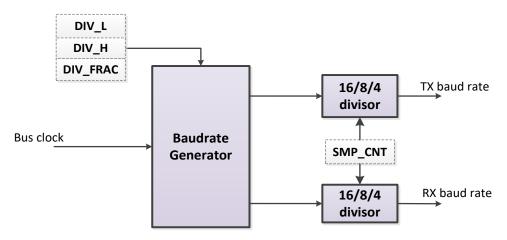

| Figure 9-13 Diagram for baud rate generator                                    |                |

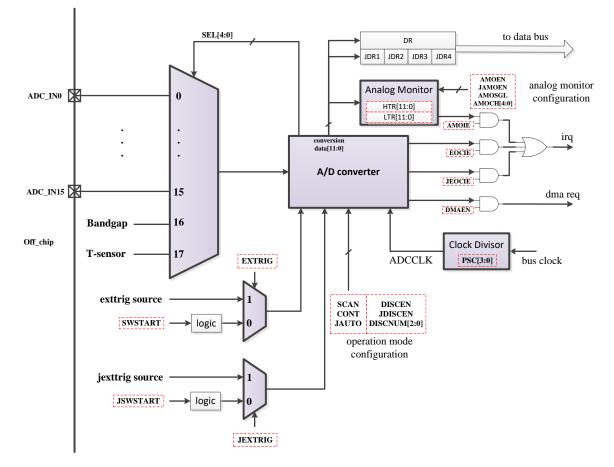

| Figure 10-1 UART block diagram                                                 |                |

| Figure 10-2 ADC Power on sequence                                              |                |

| Figure 10-3 CPU normal mode and sleep mode condition                           |                |

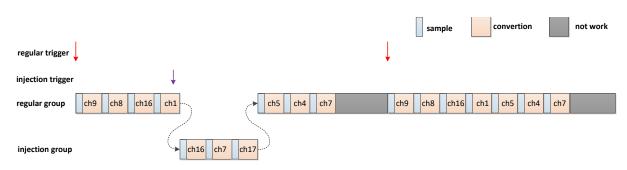

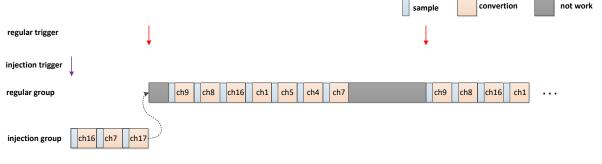

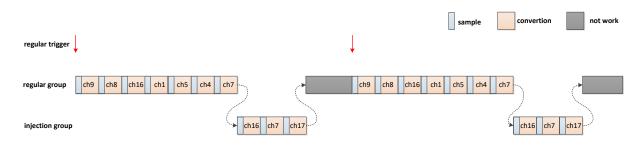

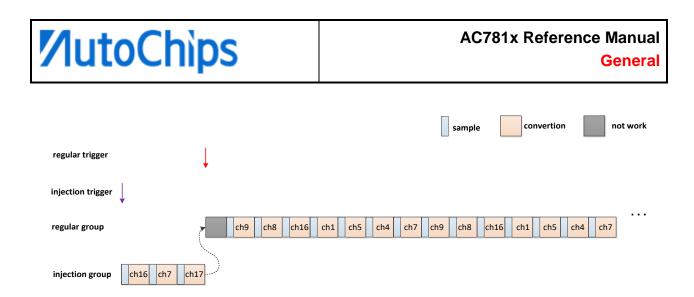

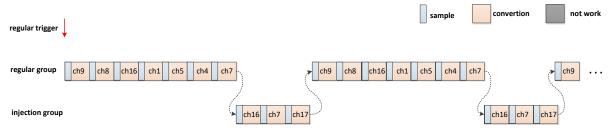

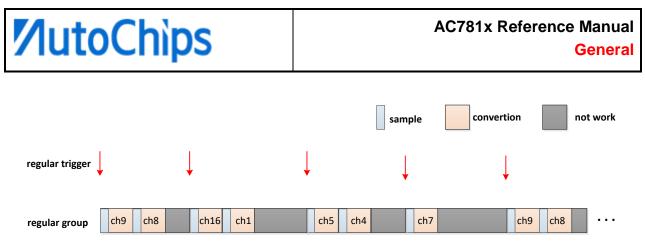

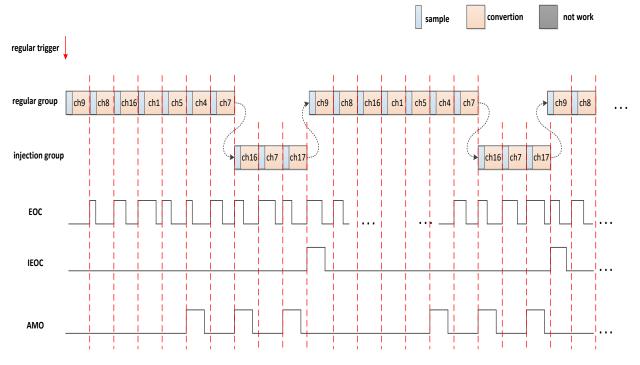

| Figure 10-4 Regular group sequence                                             |                |

| Figure 10-5 Valid regular group sequence                                       |                |

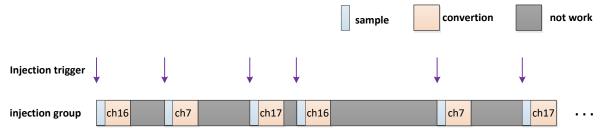

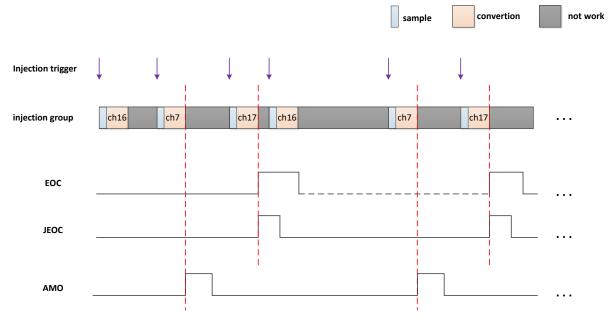

| Figure 10-6 Injection group sequence                                           |                |

| Figure 10-7 Valid injection group sequence                                     |                |

| Figure 10-8 Mode 1 operation flow                                              |                |

| Figure 10-9 Mode 2 operation flow                                              |                |

| Figure 10-10 Mode 3 typical operation flow                                     |                |

| Figure 10-11 Mode 3 operation flow with injection trigger at ADC idle state    |                |

| Figure 10-12 Mode 4 operation flow with auto injection trigger                 |                |

| Figure 10-13 Mode 5 typical operation flow                                     | 128            |

| Figure 10-14 Mode 5 operation flow with injection trigger at ADC idle state    | 129            |

| Figure 10-15 Mode 6 operation flow                                             | 129            |

| Figure 10-16 Mode 7 operation flow                                             | 130            |

| Figure 10-17 Mode 8 operation flow                                             | 130            |

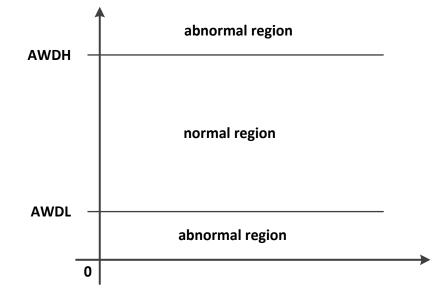

| Figure 10-18 Analog monitor detecting region                                   |                |

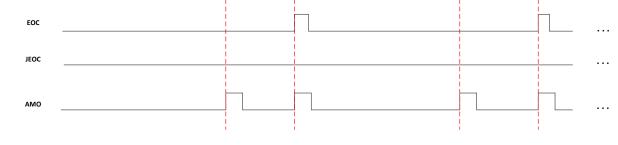

| Figure 10-19 Three flags under condition 1                                     |                |

| Figure 10-20 Three flags under condition 2                                     |                |

| Figure 10-21 Three flags under condition 3                                     |                |

| Figure 11-1 ACMP block diagram                                                 |                |

| AutoChips Confidential © 2013 - 2021 AutoChips Inc.                            | Page 16 of 360 |

| This document contains information that is proprietary to AutoChips Inc.       |                |

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

| Figure 11-2 Polling mode                                         | .144 |

|------------------------------------------------------------------|------|

| Figure 12-1 PWM block diagram                                    | .156 |

| Figure 12-2 PWM clock source                                     | .181 |

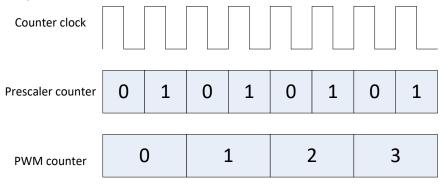

| Figure 12-3 Prescaler                                            | .182 |

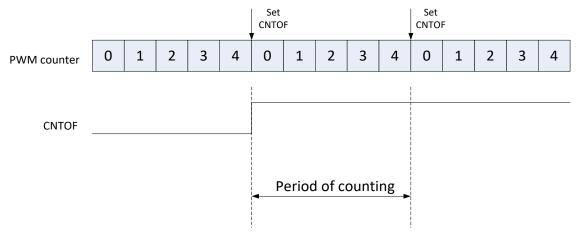

| Figure 12-4 Up counting                                          | .183 |

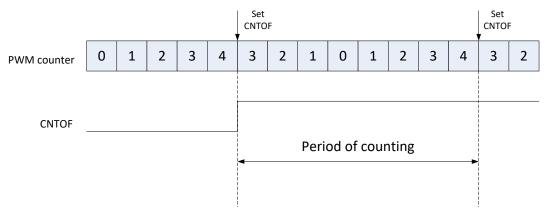

| Figure 12-5 Up-Down counting                                     |      |

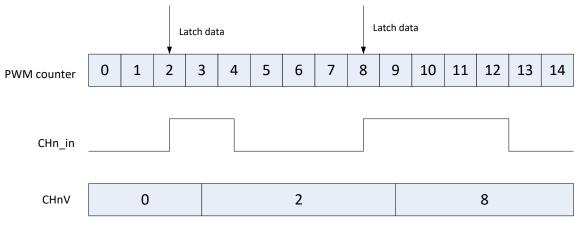

| Figure 12-6 Input Capture mode                                   |      |

| Figure 12-7 Output Compare mode                                  |      |

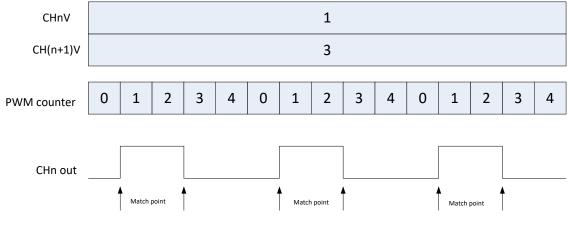

| Figure 12-8 Edge-aligned PWM mode                                | 186  |

| Figure 12-9 Center-aligned PWM mode                              | 187  |

| Figure 12-10 Combine mode                                        |      |

| Figure 12-10 Combine mode                                        |      |

|                                                                  |      |

| Figure 12-12 Dual edge capture mode                              |      |

| Figure 12-13 Features priority                                   |      |

| Figure 13-1 PWDT block diagram                                   | .197 |

| Figure 13-2 Four basic measurement modes                         |      |

| Figure 13-3 Hall measurement modes                               |      |

| Figure 13-4 Two common installation ways                         | .199 |

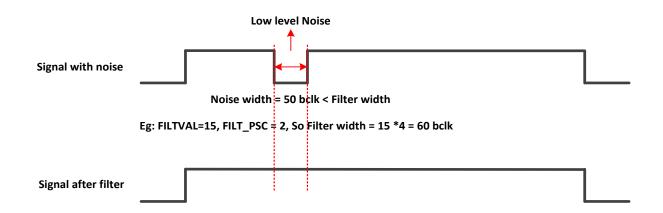

| Figure 13-5 Example for low level noise and filter               |      |

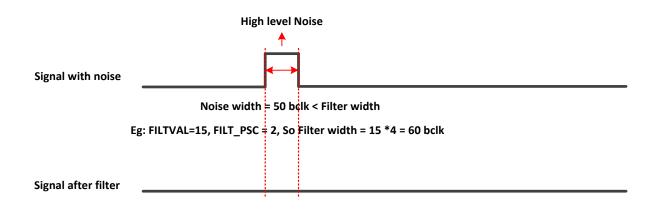

| Figure 13-6 Example for high level noise and filter              |      |

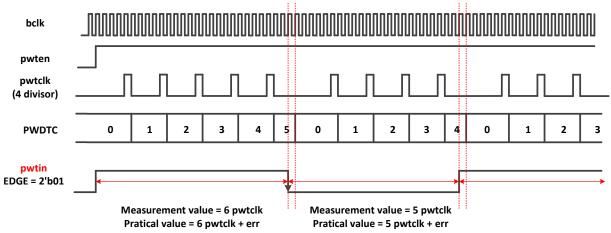

| Figure 13-7 PWDTC counter and counting error                     |      |

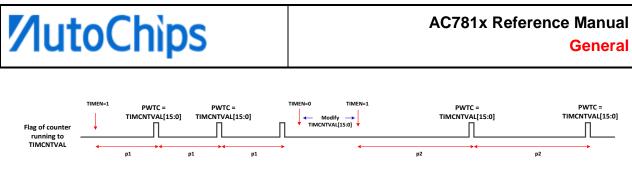

| Figure 13-8 Modify the TIMCNTVAL between the TIMEN=0 and TIMEN=1 | .201 |

| Figure 13-9 Modify the TIMCNTVAL during TIMEN=1                  | .201 |

| Figure 14-1 TIMER block diagram                                  | .205 |

| Figure 15-1 CTU block diagram                                    | .210 |

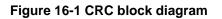

| Figure 16-1 CRC block diagram                                    |      |

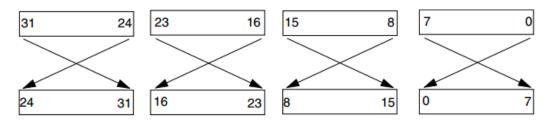

| Figure 16-2 CTRL[TOTW] / CTRL[TOTR] is 01                        |      |

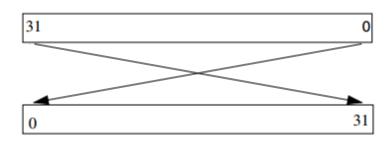

| Figure 16-3 CTRL[TOTW] / CTRL[TOTR] is 10                        |      |

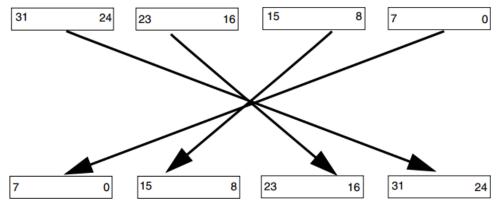

| Figure 16-4 CTRL[TOTW] / CTRL[TOTR] is 11                        |      |

| Figure 17-1 GPIO block diagram                                   |      |

| Figure 17-2 GPIO external interrupt                              |      |

| Figure 17-3 GPIO multi-function                                  |      |

| Figure 18-1 I2C block diagram                                    |      |

| Figure 18-2 Data flow of transmitter                             |      |

| Figure 18-3 Data flow of Receiver                                |      |

| Figure 18-4 START and STOP conditions                            | 240  |

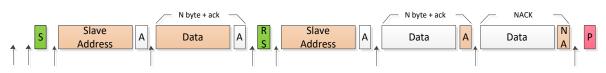

| Figure 18-5 Data transmission format                             |      |

| Figure 18-6 Baud rate generation                                 |      |

|                                                                  |      |

| Figure 18-7 BND sequence of master write slave mode              |      |

| Figure 18-8 BND sequence of master read slave mode               |      |

| Figure 18-9 Master transmitter case 1                            |      |

| Figure 18-10 Master transmitter case 2                           |      |

| Figure 18-11 Master receiver                                     |      |

| Figure 18-12 Slave transmitter                                   |      |

| Figure 18-13 Slave receiver                                      |      |

| Figure 18-14 Wakeup sequence                                     |      |

| Figure 18-15 Master write operation sequence                     |      |

| Figure 18-16 Master receiver operation sequence                  |      |

| Figure 18-17 Combined format option sequence                     |      |

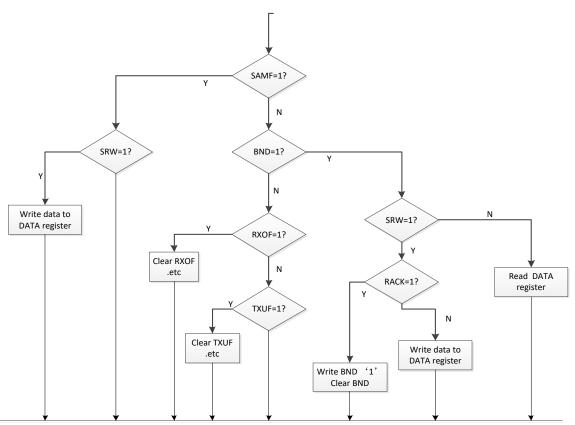

| Figure 18-18 Typical I2C slave interrupt routine                 |      |

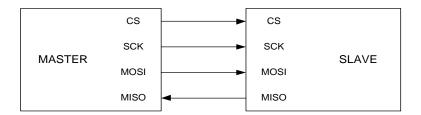

| Figure 19-1 SPI system connection                                |      |

| Figure 19-2 SPI block diagram                                    |      |

| Figure 19-3 Data flow of master                                  | .257 |

| Figure 19-4 Data flow of slave                                   |      |

| Figure 19-5 CPHA=0 Transmission Format                           |      |

| Figure 19-6 CPHA=1 Transmission Format                           |      |

| Figure 19-7 Baud rate generation                                 |      |

|                                                                  |      |

#### AutoChips Confidential

$\ensuremath{\textcircled{}}$  2013 - 2021 AutoChips Inc.

Page 17 of 360

#### AC781x Reference Manual eral

| <b>//utoChips</b>                             | AC781x Reference Manua<br>Genera |

|-----------------------------------------------|----------------------------------|

|                                               |                                  |

| Figure 19-8 SCK output timing with mode fault | t detect enable261               |

|                                               |                                  |

|                                               |                                  |

|                                               |                                  |

|                                               |                                  |

|                                               |                                  |

|                                               |                                  |

|                                               |                                  |

|                                               |                                  |

|                                               | controller                       |

|                                               | d flash controller               |

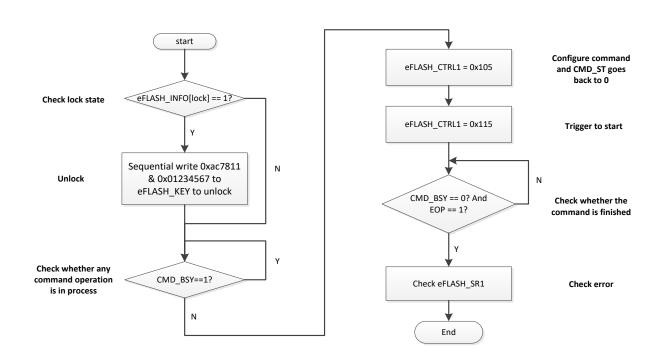

|                                               | low                              |

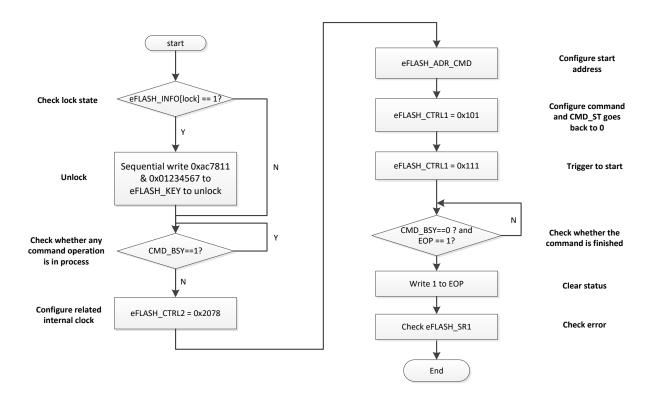

| Figure 23-4 Mass erase command operation f    | low                              |

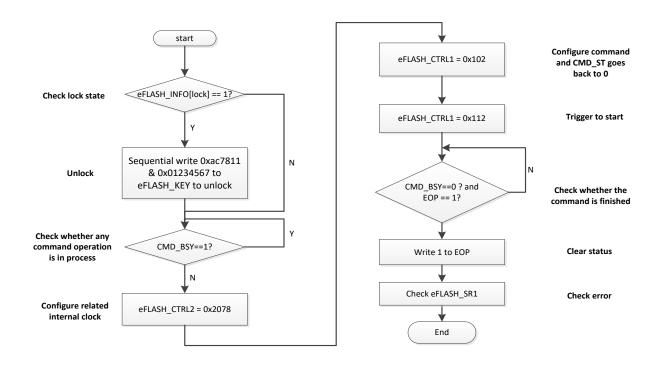

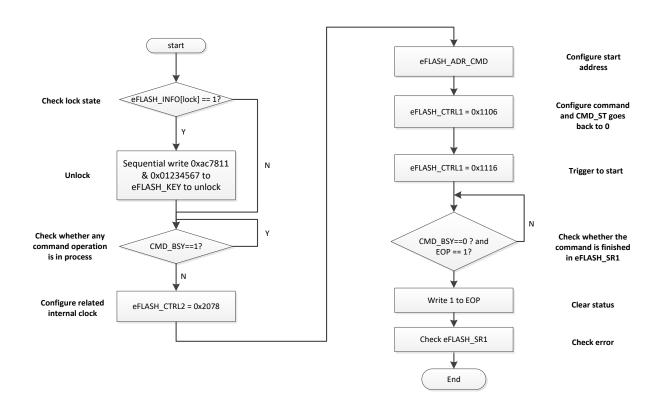

|                                               | n flow                           |

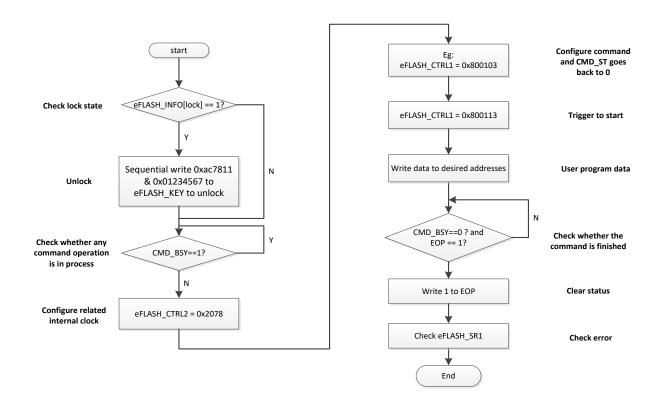

|                                               | ation flow                       |

| Figure 23-7 Mass erase verify command oper    | ation flow                       |

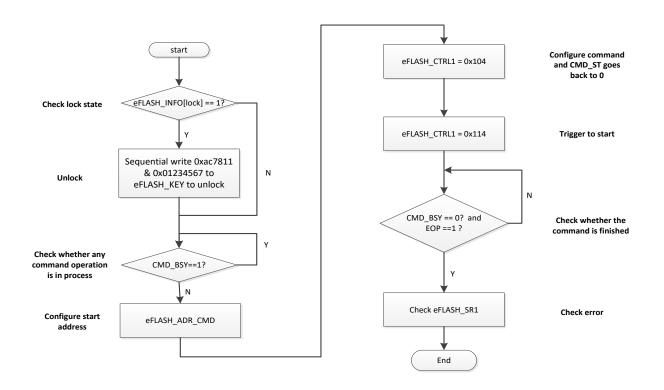

| Figure 23-8 Option page erase command ope     | ration flow                      |

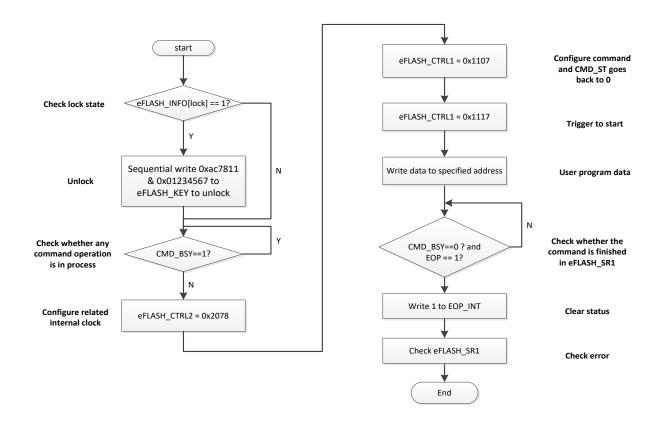

|                                               | peration flow                    |

|                                               | er                               |

|                                               |                                  |

|                                               |                                  |

|                                               |                                  |

|                                               |                                  |

|                                               | se) flow                         |

|                                               | solution 1                       |

|                                               | solution 2                       |

|                                               |                                  |

|                                               |                                  |

|                                               |                                  |

|                                               |                                  |

|                                               |                                  |

|                                               |                                  |

|                                               |                                  |

|                                               |                                  |

|                                               |                                  |

|                                               |                                  |

|                                               | 0.40                             |

# **VutoChips**

# **List of Tables**

| Table 1-1 AC781x module description                                      |           |

|--------------------------------------------------------------------------|-----------|

| Table 2-1 High-level device memory map                                   |           |

| Table 2-2 Interrupt table                                                |           |

| Table 2-3 Boot configuration                                             |           |

| Table 2-4 Address assignment of each peripheral                          |           |

| Table 3-1 Reset register map                                             |           |

| Table 4-1 Clock register map                                             |           |

| Table 5-1 Module functionality in low-power modes                        | 46        |

| Table 6-1 SPM Register Map                                               | 50        |

| Table 7-1 CAN-CRTL Register Mapping                                      | 61        |

| Table 7-2 Bits in Register ACF_3, if SELMASK=1                           |           |

| Table 7-3 Receive Buffer Registers RBUF – Standard Format (r-0)          |           |

| Table 7-4 Receive Buffer Registers RBUF – Extended Format (r-0)          | 71        |

| Table 7-5 Transmit Buffer Registers TBUF – Standard Format (rw-u)        | 71        |

| Table 7-6 Transmit Buffer Registers TBUF – Extended Format (rw-u)        | 71        |

| Table 7-7 Control bits in RBUF and TBUF                                  | 72        |

| Table 7-8 Definition of the DLC (according to the CAN 2.0 specification) | 72        |

| Table 7-9 Software reset                                                 | 81        |

| Table 7-10 CAN Timing Segments                                           |           |

| Table 7-11 CAN-CTRL Timing Settings                                      |           |

| Table 7-12 Sample settings for 48MHz can_clk                             |           |

| Table 7-13 Sample settings for 8MHz can_clk                              |           |

| Table 8-1 LIN interrupt table                                            |           |

| Table 8-2 LIN register map                                               |           |

| Table 9-1 Function classification and configuration                      |           |

| Table 9-2 UART input&output timing                                       |           |

| Table 9-3 Typical baud rate and error@bclock=50MHz                       |           |

| Table 9-4 Typical baud rate and error @bclock=36MHz                      |           |

| Table 9-5 UART register map                                              |           |

| Table 10-1 Power modes                                                   |           |

| Table 10-2 ADC operation modes and its corresponding configuration       |           |

| Table 10-3 Analog monitor configuration                                  |           |

| Table 10-4 ADC register map                                              |           |

| Table 11-1 ACMP register map                                             |           |

| Table 11-2 ACMP interrupt table                                          |           |

| Table 12-1 PWM modules configuration                                     |           |

| Table 12-2 PWM register map and reset values                             |           |

| Table 12-3 Operation mode configuration                                  |           |

| Table 12-4 PWM_CNTIN register update buffer                              |           |

| Table 12-5 PWM_CH(n)V register update buffer                             |           |

| Table 12-6 PWM_MCVR register update buffer                               | 189       |

| Table 12-7 Software output control when COMP bit is zero                 |           |

| Table 12-8 Software output control when COMP bit is one                  |           |

| Table 12-9 Fault source and number table                                 |           |

| Table 13-1 Measurable pulse width range                                  |           |

| Table 13-2 Filterable pulse width range                                  |           |

| Table 13-3 PWDT register map and reset values                            |           |

| Table 14-1 TIMER register map                                            |           |

| Table 15-1 ADC hardware trigger1 source                                  |           |

| Table 15-2 CTU register map                                              |           |

| Table 16-1 CRC register map                                              |           |

| Table 17-1 GPIO multi-function                                           |           |

| Table 17-2 GPIO register map                                             |           |

|                                                                          | 19 of 360 |

|                                                                          | 10 01 000 |

This document contains information that is proprietary to AutoChips Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

| Table 18-1 I2C register map                                      | 239 |

|------------------------------------------------------------------|-----|

| Table 18-1 I2C register map         Table 18-2 Interrupt summary | 252 |

| Table 19-1 Interrupt summary                                     |     |

| Table 19-2 SPI register map                                      |     |

| Table 20-1 DMA request mapping                                   | 270 |

| Table 20-2 Programmable data width & data alignment              | 273 |

| Table 20-3 DMA register map                                      | 273 |

| Table 21-1 WDG register map                                      |     |

| Table 22-1 RTC register map                                      |     |

| Table 23-1 Flash memory organization                             |     |

| Table 23-2 The content of the key addresses in option page       |     |

| Table 23-3 Read protection description                           |     |

| Table 23-4 Write protection description                          |     |

| Table 23-5 Watch dog enable description                          |     |

| Table 23-6 Embedded flash register map                           |     |

| Table 24-1 Clock configuration register                          |     |

| Table 24-2 Flashif related register map                          |     |

### 1 Introduction

**NutoChips**

#### 1.1 Overview

This chapter provides an overview of AC781x. It also presents high level descriptions of the modules. AC781x is a high-performance, low-power MCU with ARM Cortex<sup>™</sup>-M3 core.

- Up to 100 MHz CPU frequency

- Temperature range (ambient): -40°C to +125°C

- Voltage range: 2.7 V to 5.5 V

### **1.2 Module description**

#### Table 1-1 AC781x module description

| Module              | Descriptions                                                        |

|---------------------|---------------------------------------------------------------------|

| ARM Cortex CM3 core | 32-bit MCU core from ARM's Cortex-M class                           |