# autochips

## AC7803x 数据手册

适用于以下产品:

AC78036HFLA, AC78036FFLA, AC78036HELA, AC78036FELA, AC78036HDLA, AC78036FDLA

文档版本: 1.0.1

发布日期: 2025-03-28

© 2013 - 2024 杰发科技

本文档包含杰发科技的专有信息。未经授权,严禁复制或披露本文档包含的任何信息。由于产品版本升级或其他原因,本文档内容会不定期进行更新。

## 修订记录

| 版本    | 日期         | 作者        | 描述     |

|-------|------------|-----------|--------|

| 1.0.0 | 2024-06-17 | AutoChips | 正式版    |

| 1.0.1 | 2025-03-28 | AutoChips | 修改丝印信息 |

|       |            |           |        |

|       |            |           |        |

|       |            |           |        |

## 版权声明

本数据手册包含杰发科技的机密信息。禁止未经授权使用或披露本手册包含的信息。对因未经杰发科技授权而全部或部分披露此文档内容而给杰发科技带来的任何损失或损害,杰发科技将追究责任。

杰发科技保留对此处任何信息进行更改的权利,此处的信息如有变更,恕不另行通知。杰发科技对使用 或依赖此处包含的信息不承担任何责任。

本数据手册的所有信息均"按原样"提供,不提供任何形式的明示、暗示、法定或其他形式的保证。杰发科技明确拒绝对适销性,非侵权性和针对特定用途的适用性方面的的所有暗示保证。杰发科技对本手册可能使用、包含或提供的任何第三方软件不提供任何担保,并且用户同意仅向该等第三方寻求与此相关的任何担保索赔。杰发科技对于根据用户规格或为符合特定标准或公开论坛而产生的任何交付物,也不承担任何责任。

## 文档目录

| 修订 | 记录…   |               |                              | 2     |

|----|-------|---------------|------------------------------|-------|

| 版权 | 声明    |               |                              | 3     |

| 文档 | 目录    |               |                              | 4     |

|    |       |               |                              |       |

|    |       |               |                              |       |

|    |       |               |                              |       |

| 1  |       |               |                              |       |

| 2  |       |               |                              |       |

| 3  | 器件    | 标识            |                              | 11    |

|    | 3.1   | 说明            |                              | 11    |

|    | 3.2   |               |                              |       |

|    | 3.3   | •             |                              |       |

|    | 3.4   | 示例            |                              | 12    |

| 4  | 参数    | 分类            |                              | 13    |

| 5  | 额定    | 值             |                              | 14    |

|    | 5.1   | 热学操作          | 三额定值                         | 14    |

|    | 5.2   |               |                              |       |

|    | 5.3   |               |                              |       |

|    | 5.4   |               | <br>l.流操作额定值                 |       |

| 6  | 通用    |               |                              | 16    |

| Ü  | 6.1   |               | . 规格                         |       |

|    | 0.1   | 6.1.1         | 电源和地引脚                       |       |

|    |       | 6.1.2         | DC 特性                        |       |

|    |       | 6.1.3         | 电源电流特性                       |       |

|    | 6.2   | 动态规格          |                              |       |

|    |       | 6.2.1         | 控制时序                         |       |

|    |       | 6.2.2         | PWM 模块时序                     | 20    |

|    | 6.3   | 热规格           |                              | 21    |

|    |       | 6.3.1         | 热特性                          | 21    |

| 7  | 外设    | 工作要求和         | 印行为                          | 23    |

|    | 7.1   | 内核模块          | 1                            | 23    |

|    |       | 7.1.1         | SWD 电气规格                     |       |

|    | 7.2   | 外部振荡          | 5器 (OSC) 和内部时钟源(ICS) 特性      | 23    |

|    |       | 7.2.1         | 外部高速振荡器(HFXOSC) 特性           | 23    |

|    |       | 7.2.2         | 外部低速振荡器(LFXOSC) 特性           | 24    |

|    |       | 7.2.3         | 内部 RC 特性                     |       |

|    |       | 7.2.4         | PLL 特性                       |       |

|    | 7.3   |               | sh 规格                        |       |

|    | 7.4   |               |                              |       |

|    |       | 7.4.1         | ADC 特性                       |       |

|    |       | 7.4.2         | 模拟比较器(ACMP)和数模转换器电气规格        |       |

|    | 7.5   |               | CDI +0-1/2                   |       |

|    |       | 7.5.1         | SPI 规格                       |       |

|    |       | 7.5.2 $7.5.3$ | UART 规格<br>CAN 规格            |       |

| 木化 | 拟牡牡   | 7.3.3<br>l密文件 | © 2013- 2024 杰发科技有限公司        |       |

| 灬汉 | イナコメリ | 山山人口          | ◎ 4010- 4044 (広及/門)又(門)(広 円) | 4 /40 |

# autochips

## AC7803x 数据手册 通用版

|   |     | 7.5.4  | I2C 规格   | 31 |

|---|-----|--------|----------|----|

|   |     |        | EIO 规格   |    |

| 8 | 尺寸  | •••••  |          | 34 |

|   |     |        | 封装信息     |    |

|   | 8.2 | LQFP64 | 封装信息     | 37 |

| 9 | 引脚: | 分配     |          | 40 |

|   | 9.1 | 信号多路   | 6复用和引脚分配 | 40 |

|   |     |        | ]分配      |    |

## 插图目录

| 图 | 2-1 | AC7803x 整体框图                                        | 10 |

|---|-----|-----------------------------------------------------|----|

| 冬 | 6-1 | 电压引脚去耦                                              | 16 |

| 冬 | 6-2 | 定时器输入捕捉脉冲                                           | 21 |

| 冬 | 7-1 | 典型晶振或振荡器电路                                          | 24 |

| 图 | 7-2 | ADC 输入等效图                                           | 27 |

| 图 | 7-3 | ACMP 迟滞示意图                                          | 28 |

| 图 | 7-4 | SPI 时序图 —主机                                         | 29 |

| 图 | 7-5 | SPI 时序图 -从机(cpha=0)                                 | 30 |

| 图 | 7-6 | SPI 时序图 -从机(cpha=1)                                 | 30 |

| 图 | 7-7 | 标准与快速模式下 I2C 总线时序图                                  | 33 |

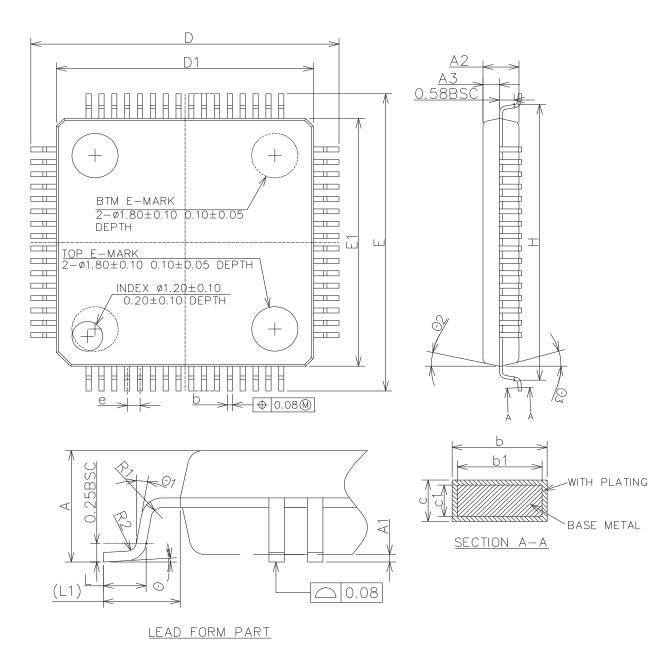

| 图 | 8-1 | $LQFP-48$ 引脚, $7 \times 7$ 毫米薄行低轮廓四方引脚扁平式封装外形 [1]   | 34 |

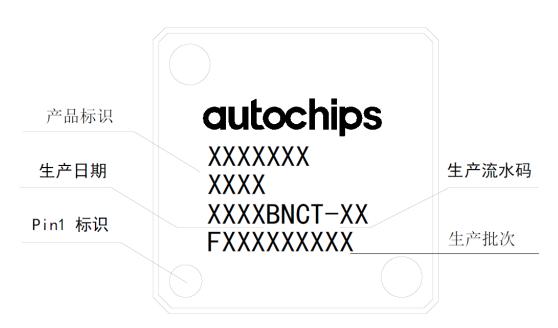

| 图 | 8-2 | LQFP48 正印示例 (封装顶视图)                                 | 36 |

| 冬 | 8-3 | $LQFP-64$ 引脚, $10 \times 10$ 毫米薄行低轮廓四方引脚扁平式封装外形 [1] | 37 |

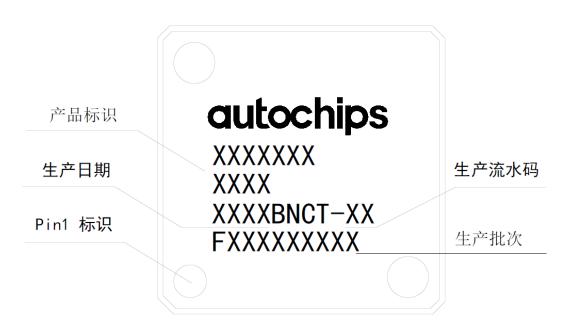

| 冬 | 8-4 | LQFP64 正印示例 (封装顶视图)                                 | 39 |

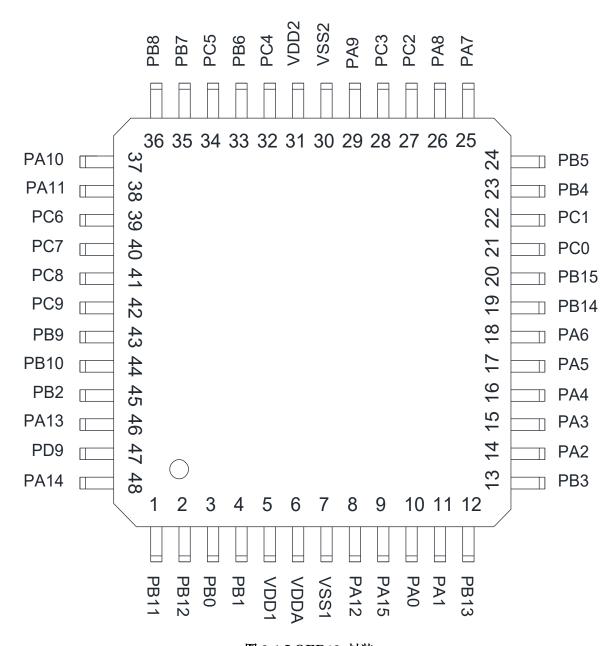

| 冬 | 9-1 | LQFP48 封装                                           | 42 |

| 图 | 9-2 | LQFP64 封装                                           | 43 |

# autochips

## 表格目录

| 表 3-1 器件编号字段说明                                                     | 11 |

|--------------------------------------------------------------------|----|

| 表 4-1 参数分类                                                         | 13 |

| 表 5-1 热学操作额定值                                                      |    |

| 表 5-2 湿度操作额定值                                                      | 14 |

| 表 5-3 ESD 操作额定值                                                    | 14 |

| 表 5-4 电压和电流操作额定值                                                   | 15 |

| 表 6-1 DC 特性                                                        | 17 |

| 表 6-2 LVD /POR / AVDD 电压告警规格                                       | 18 |

| 表 6-3 供电电流特性                                                       | 19 |

| 表 6-4 控制时序                                                         | 20 |

| 表 6-5 PWM 输入时序                                                     | 21 |

| 表 6-6 热学属性                                                         | 21 |

| 表 7-1 SWD 全电压范围电气规格                                                | 23 |

| 表 7-2 OSC 规格 (环境温度范围 = -40 至 125 °C)                               | 23 |

| 表 7-3 OSC 规格 (环境温度范围 = -40 至 125 °C)                               | 24 |

| 表 7-4 OSC 和 ICS 规格 (环境温度范围 = -40 至 125 °C)                         | 25 |

| 表 7-5 PLL 特性                                                       | 25 |

| 表 7-5 片内 Flash 特性                                                  | 25 |

| 表 7-6 12 位 ADC 和温度传感器工作条件和特性                                       | 26 |

| 表 7-7 12 位 ADC 和温度传感器工作条件和特性(续)                                    | 27 |

| 表 7-8 比较器电气规格                                                      | 28 |

| 表 7-9 SPI 特性 - 主机                                                  | 29 |

| 表 7-10 SPI 特性 - 从机                                                 | 30 |

| 表 7-11 CAN 唤醒脉冲特性                                                  |    |

| 表 7-12 不同模式下 I2C 总线特性                                              |    |

| 表 8-1 LQFP – 48 引脚, 7x7毫米薄行低轮廓四方引脚扁平式封装外形机械数据 ⑴                    |    |

| 表 8-2 LQFP – 64 引脚, $10 \times 10$ 毫米薄行低轮廓四方引脚扁平式封装外形机械数据 $^{[1]}$ | 38 |

| 表 9-1 信号多路复用和引脚分配表 [2]                                             | 40 |

# autochips

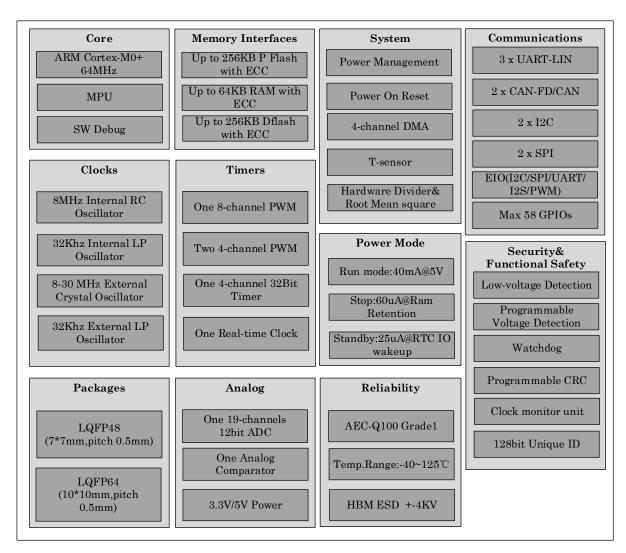

## 1 主要特性

#### • 车规标准

➤ 支持 AEC-Q100 Grade 1

#### 性能

- ➤ 高达 64 MHz 的 ARM® Cortex-M0+内核

- ▶ 单周期 32 位乘法器

- ▶ 快速 I/O 访问接口

#### • 存储器和存储器接口

- ▶ 内置 2 个 256 KB Flash with ECC (256KB DFlash 和 256KB PFlash)

- ➤ 64 KB 的 SRAM with ECC

#### • 时钟

- ▶ 外部高速振荡器(HFXOSC) 支持 8 MHz 到 30 MHz 石英晶体振荡 器;可选择低功耗或高增益振荡器

- ▶ 外部低速振荡器 (LFXOSC)

- ▶ 内部时钟源 (LFOSC) 内部 RC 振荡器提供 8 MHz 时钟源

- ▶ 内部 32 KHz 低功耗振荡器 (LPO)

- ▶ 内部 PLL

#### • 系统外设

- ▶ 电源管理模块(SPM) 有三个功率 模式: run mode, stop mode, standby mode

- ▶ 低压检测复位电路 (LVD)

- ▶ 带独立时钟源的看门狗(WDG)

- ▶ 串行线调试(SWD)接口

#### • 人机接口

- ▶ 最多 58 个通用输入输出接口 (GPIO)

- ▶ 支持外部中断 (IRQ)模块

#### • 模拟模块

- ▶ 1 个多达 19 通道、12 位 0.8Msps 的 SAR ADC,可选硬件触发器 (ADC)

- ▶ 1个包含8位DAC和可编程参考输入的模拟比较器(ACMP)

#### • 定时器

- ➤ 两个 4 通道和一个 8 通道互补脉宽 调制 (PWM) 单元

- ▶ 1个四通道 32bit 周期性中断定时器 (TIMER)

- ▶ 2个脉冲宽度检测定时器(PWDT)

- ▶ 1个实时时钟 (RTC)

#### • 通信接口

- ➤ 3 个 UART 模块 (3 路均支持 Software LIN)

- ▶ 2 个 SPI 模块

- ▶ 2 个 I2C 模块

- ▶ 2 个 CAN-FD 模块,兼容 CAN

# autochips

▶ 1 个 EIO 模块 (增强型 IO)

#### • 操作特性

- ▶ 电压范围: 2.7 到 5.5 V

- ▶ 温度范围 (环境): -40 到 125°C

#### • 封装选项

- ➤ 64 引脚 LQFP

- ➤ 48 引脚 LQFP

#### • 信息安全&功能安全

- ▶ 支持低压检测复位电路(LVD)

- ▶ 支持可编程电压检测(PVD)

- ▶ 支持可编程 CRC

- ▶ 内存保护单元

- ▶ 支持时钟监控单元(CMU)

- ▶ 独立时钟源的看门狗(WDG)

- ▶ 支持 128bit 唯一 ID

## 2 整体框图

图 2-1 AC7803x 整体框图

## 3 器件标识

### 3.1 说明

芯片器件型号包含可识别具体器件的字段。您可以使用这些字段的值来区分收到的具体器件。

### 3.2 格式

此设备的器件编号采用如下格式:

AC####HFLA

## 3.3 字段

下表列出器件编号中每个字段的可能值(并非所有组合都有效)。

表 3-1 器件编号字段说明

| 字段 | 说明                 | 值                                 |

|----|--------------------|-----------------------------------|

| AC | AutoChips          | · AC                              |

| 7  | AutoChips mcu 系列   | • 7                               |

| 8  | 汽车通用型              | • 8                               |

| 0  | Core Platform      | • 0 = Cortex-M0+                  |

| 3  | 特定功能位              | • 3:平台系列                          |

| 6  |                    | • 6:平台子系列:                        |

| Н  | 引脚数目               | • P: 20 • M: 32 • F: 48           |

|    |                    | • H:64 • L:100 • Y:144            |

|    |                    | • U:176                           |

| F  | Flash 存储器大小        | • A = 16KB • B = 32KB             |

|    |                    | • $C = 64KB$ • $D = 128KB$        |

|    |                    | • $E = 256KB$ • $Z = 448KB$       |

|    |                    | • F = 512KB                       |

| L  | 封装类型               | • L = LQFP                        |

|    |                    | • Q = QFN                         |

|    |                    | • T = TSSOP                       |

| A  | 温度范围(°C)           | • A = AEC-Q100 Grade 1(-40~125°C) |

|    |                    | • I = -40~105°C                   |

| /x | 内部标识用,仅包装 P/N 后缀用到 | /A 或/B 等                          |

11/43

## 3.4 示例

器件编号示例为: AC78036HFLA。

## 4 参数分类

下表中显示的电气参数通过不同的方法来保证达到要求。为了便于客户更好地理解,将使用如下的分类,并在表中适当的位置相应标记参数。

#### 表 4-1 参数分类

| P | 在对每个设备进行生产测试时确保达到这些参数要求。                                  |

|---|-----------------------------------------------------------|

| С | 通过不同制程的、具有统计意义的相关样本数量的测量结果来保证这些参数要求。                      |

| Т | 除非另有说明,否则通过统计典型条件下典型器件的小规模样本测量值来保证这些参数要求。此类别包含典型列中所示的所有值。 |

| D | 这些参数主要来自于仿真。                                              |

## 5 额定值

## 5.1 热学操作额定值

表 5-1 热学操作额定值

| 符号   | 说明       | 最小值 | 最大值 | 单位                   | 附注 |

|------|----------|-----|-----|----------------------|----|

| TSTG | 存储温度     | -55 | 150 | $^{\circ}\mathrm{C}$ | 1  |

| TSDR | 焊接温度, 无铅 | _   | 260 | $^{\circ}\mathrm{C}$ | 2  |

- 1. 根据 JEDEC JESD22-A103 标准中"高温存储寿命"来确定。

- 2. 根据 IPC/JEDEC J-STD-020 标准中"非密封固态表面贴装设备湿度/再流焊灵敏度分类"确定。

### 5.2 湿度操作额定值

表 5-2 湿度操作额定值

| 符号  | 说明      | 最小值 | 最大值 | 单位 | 附注 |

|-----|---------|-----|-----|----|----|

| MSL | 湿度灵敏度级别 |     | 3   |    | 1  |

1. 根据 IPC/JEDEC J-STD-020 标准中"非密封固态表面贴装设备湿度/再流焊灵敏度分类"确定。

### 5.3 ESD 操作额定值

表 5-3 ESD 操作额定值

| 符号                 | 说明               | 最小值   | 最大值  | 单位 | 附注 |

|--------------------|------------------|-------|------|----|----|

| $V_{\mathrm{HBM}}$ | 静电放电电压, 人体放电模式   | -4000 | 4000 | V  | 1  |

| V <sub>CDM</sub>   | 静电放电电压, 设备充电模式   | -750  | 750  | V  | 2  |

| ILAT               | 125°C 温度环境下的闩锁电流 | -100  | 100  | mA | 3  |

- 1. 根据 AEC-Q100-002-D,HUMAN BODY MODEL ELECTROSTATIC DISCHARGE TEST 来确定。

- 2. 根据 AEC-Q100-011-C1,CHARGED DEVICE MODEL (CDM) ELECTROSTATIC DISCHARGE TEST 确定。

- 3. 根据 AEC-Q100-004-D,IC LATCH-UP TEST 确定。

- 在 125 °C 环境温度下进行测试(II 类);

- 电源组 1.5 Vccmax

## 5.4 电压和电流操作额定值

绝对最大额定值仅为应力额定值,并不保证最大值时的功能操作。超过下表中指定的应力可能影响器件的可靠性或对器件造成永久性损坏。有关功能操作条件的更多信息,请参考此文档中的其他表格。

该器件包含防止高静态电压或电场造成损坏的电路,但建议采取预防措施,以避免实际应用中高于额定电压的输入造成这部分电路的损坏。未用输入引脚连接到适当的逻辑电压电平(例如,Vss 或 VDD)或使能相关引脚的内部上拉电阻,可增强操作的可靠性。

表 5-4 电压和电流操作额定值

| 符号                | 说明                       | 最小值  | 最大值                    | 单位 |

|-------------------|--------------------------|------|------------------------|----|

| $V_{\mathrm{DD}}$ | 外部电源电压                   | 2.7  | 5.5                    | V  |

| $I_{DD}$          | 流入 V <sub>DD</sub> 的最大电流 | _    | 60                     | mA |

| V <sub>IN</sub>   | 除开漏引脚之外的输入电压             | -0.3 | $V_{DD} + 0.3$ [1]     | V  |

|                   | 开漏引脚的输入电压                | -0.3 | $V_{\rm DD}$ + 0.3 [1] | V  |

| $I_D$             | 单引脚瞬态最大电流限值(适用于所有端口引脚)   | -16  | 16                     | mA |

<sup>[1]</sup> 最大额定  $V_{DD}$  也适用于  $V_{IN}$ 。

## 6 通用

### 6.1 静态电气规格

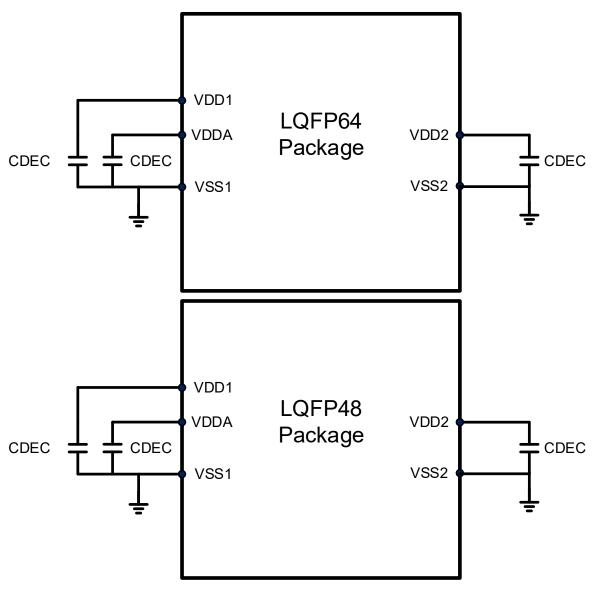

#### 6.1.1 电源和地引脚

图 6-1 电压引脚去耦

- 1. VDD1 和 VDD2 在板上需连接到同一个供电电源。

- 2. 所有的退耦电容都需要使用 X7R 类型的低 ESR 值陶瓷电容, 电容值建议是 0.1 uF。

- 3. 为了使电源引脚有更好的性能,建议使用 10 uF、0.1 uF 和 1 nF 电容并联形成退耦网络。

4. 所有的退耦电容都必须尽可能地靠近相应的电源和地引脚放置。

#### 6.1.2 DC 特性

本节包括有关电源要求和 I/O 引脚特性的信息。

表 6-1 DC 特性

| 符号              | C | 说明    |                            |                                                       | 最小值                  | 典型值 | 最大值                  | 单位 |

|-----------------|---|-------|----------------------------|-------------------------------------------------------|----------------------|-----|----------------------|----|

| _               | _ | 工作电压  |                            | _                                                     | 2.7                  | _   | 5.5                  | _  |

| V <sub>OH</sub> | P | 输出高电压 | 驱动强度                       | 5 V, I <sub>load</sub> = -4,<br>-8, -12, -16mA        | V <sub>DD</sub> -0.8 | _   | _                    | V  |

|                 | С |       |                            | 3 V, I <sub>load</sub> = -3.6,<br>-7.2,-10.8,-14.4 mA | V <sub>DD</sub> -0.8 | _   | _                    | V  |

| Іонт            | D | 输出高电压 | 所有端口的<br>最大总输出<br>高电流 Ioн  | 2.7≤V <sub>DD</sub> <5.5 V                            | _                    | _   | 50                   | mA |

| V <sub>OL</sub> | Р | 输出低电压 | 驱动强度                       | 5 V, I <sub>load</sub> = 4,<br>8, 12, 16mA            | _                    | _   | 0.8                  | V  |

|                 | С |       |                            | 3 V, I <sub>load</sub> = 3.6,<br>7.2,10.8,14.4 mA     | _                    | _   | 0.8                  | V  |

| Iolt            | D | 输出低电压 | 所有端口的<br>最大总输出<br>低电流 IoL  | 2.7≤V <sub>DD</sub> <5.5 V                            | _                    | _   | 50                   | mA |

| V <sub>IH</sub> | P | 输入高电压 | 全部数字输入                     | 4.5≤V <sub>DD</sub> <5.5 V                            | 0.65×V <sub>DD</sub> | _   | $V_{\rm DD}$ + 0.3   | V  |

|                 |   |       |                            | 2.7≤V <sub>DD</sub> <4.5 V                            | $0.70 \times V_{DD}$ | _   | $V_{\rm DD} + 0.3$   |    |

| $V_{ m IL}$     | P | 输入低电压 | 全部数字输入                     | 4.5≤V <sub>DD</sub> <5.5 V                            | -0.3                 | _   | $0.35 \times V_{DD}$ | v  |

|                 |   |       |                            | 2.7≤V <sub>DD</sub> <4.5 V                            | -0.3                 | _   | 0.30×V <sub>DD</sub> |    |

| $V_{ m hys}$    | С | 输入迟滞  | 全部数字输入                     | _                                                     | 0.06×V <sub>DD</sub> | _   | _                    | V  |

| I <sub>In</sub> | P | 输入漏电流 | 每个引脚 (高<br>阻抗输入模<br>式下的引脚) | V <sub>IN</sub> = V <sub>DD</sub> 或 V <sub>SS</sub>   | -1                   | 0.1 | 1                    | uA |

| R <sub>PU</sub> | P | 上拉电阻  | 所有数字输<br>入并使能内<br>部上拉      | _                                                     | 40                   | 75  | 150                  | kΩ |

| R <sub>PD</sub>            | P | 下拉电阻    | 所有数字输<br>入并使能内<br>部下拉      | _                                                                                  | 40       | 75 | 150 | kΩ |

|----------------------------|---|---------|----------------------------|------------------------------------------------------------------------------------|----------|----|-----|----|

| IIC                        | D | DC 注入电流 | 单引脚限值<br>总 MCU 限<br>值,包括所有 | $\begin{array}{c} V_{\rm IN} < V_{\rm SS}, V_{\rm IN} > \\ V_{\rm DD} \end{array}$ | -2<br>-5 | _  | 2   | mA |

|                            |   |         | 应力引脚的 总和                   |                                                                                    |          |    | 30  |    |

| $\mathrm{C}_{\mathrm{In}}$ | С | 输入电容, 所 | 有引脚                        | _                                                                                  | _        | 5  | 7   | pF |

| $V_{\rm RAM}$              | С | RAM 保留电 | 压                          | _                                                                                  | 2.3      | _  | _   | V  |

#### 表 6-2 LVD /POR / AVDD 电压告警规格

| 符号                    | C | 说明                         | 最小值  | 典型值 | 最大值  | 单位 |

|-----------------------|---|----------------------------|------|-----|------|----|

| V <sub>POR</sub>      | D | POR 重置电压 [1]               | 1.9  | 2.1 | 2.3  | V  |

| V <sub>L</sub> VRL    | С | 下降沿低压检测阀值—低档位(LVDV=0)      | 2.5  | 2.6 | 2.7  | V  |

| $ m V_{LVRH}$         | С | 下降沿低压检测阀值—高档位 (LVDV=1) [2] | 4.2  | 4.3 | 4.4  | V  |

| V <sub>HYSLVR</sub>   | С | 低电压复位迟滞凹                   | _    | 50  | _    | mV |

| $V_{ m LVDL}$         | С | 下降沿低电压告警阀值—低档位             | 2.8  | 2.9 | 3.0  | V  |

| $V_{\rm LVDH}$        | С | 下降沿低电压告警阀值—高档位             | 4.5  | 4.6 | 4.7  | V  |

| $V_{\mathrm{HYSLVD}}$ | С | 低电压告警迟滞                    | _    | 50  | _    | mV |

| $V_{\mathrm{BG}}$     | P | 经过缓冲的带隙输出 [3]              | 1.18 | 1.2 | 1.22 | V  |

- [1] 最大值是 POR 可以保证的最高电压值;

- [2] 迟滞电压=上升沿阀值-下降沿阀值;

- [3] 电压已在  $V_{DD}$  = 5.0 V,Temp = 25 °C 下进行出厂调整。

#### 6.1.3 电源电流特性

表 6-3 供电电流特性

| 参数                                                      | 符号                          | 内核/总线频<br>率 | V <sub>DD</sub> (V) | -40℃  | 25℃<br>[1] | 85℃   | 105℃  | 125℃  | 单位  |

|---------------------------------------------------------|-----------------------------|-------------|---------------------|-------|------------|-------|-------|-------|-----|

| LFOSC(8M), all modules                                  |                             | 8/8 MHz     | 5                   | 3.783 | 3.931      | 4.237 | 4.517 | 4.858 |     |

| clocks enabled                                          | $ m RI_{DD}$                | 8/8 MHz     | 3.3                 | 3.77  | 3.929      | 4.234 | 4.486 | 4.823 | mA  |

| LFOSC(8M), all modules                                  | DI                          | 8/8 MHz     | 5                   | 2.555 | 2.683      | 2.975 | 3.255 | 3.595 | 4   |

| clocks disabled                                         | $RI_{DD}$                   | 8/8 MHz     | 3.3                 | 2.545 | 2.683      | 2.974 | 3.22  | 3.558 | mA  |

| LFOSC(8M)+PLL, all                                      | DI                          | 64/32 MHz   | 5                   | 21.33 | 22.07      | 22.89 | 23.25 | 23.73 | A   |

| modules clocks enabled                                  | $ m RI_{DD}$                | 64/32 MHz   | 3.3                 | 21.24 | 22.05      | 22.82 | 23.22 | 23.59 | mA  |

| LFOSC(8M)+PLL, all                                      | DI                          | 64/32 MHz   | 5                   | 16.05 | 16.74      | 17.5  | 17.85 | 18.34 | mA  |

| modules clocks disabled                                 | $ m RI_{DD}$                | 64/32 MHz   | 3.3                 | 15.98 | 16.69      | 17.43 | 17.83 | 18.2  | mA  |

|                                                         |                             | 64/32 MHz   |                     | 23.33 | 24.24      | 25.32 | 25.81 | 26.45 |     |

|                                                         |                             | 24/24 MHz   |                     | 16.03 | 16.86      | 17.88 | 18.36 | 19    |     |

|                                                         |                             | 12/12 MHz   | 5                   | 12.64 | 13.43      | 14.41 | 14.89 | 15.52 |     |

| XOSC+PLL,                                               | $\mathrm{RI}_{\mathrm{DD}}$ | 8/8 MHz     |                     | 9.374 | 10.13      | 11.06 | 11.53 | 12.15 |     |

| all modules clocks enabled                              |                             | 64/32 MHz   |                     | 23.25 | 24.15      | 25.23 | 25.78 | 26.25 | mA  |

|                                                         |                             | 24/24 MHz   | 3.3                 | 15.95 | 16.76      | 17.8  | 18.33 | 18.81 |     |

|                                                         |                             | 12/12 MHz   |                     | 12.55 | 13.33      | 14.33 | 14.85 | 15.34 |     |

|                                                         |                             | 8/8 MHz     |                     | 9.284 | 10.02      | 10.98 | 11.49 | 11.98 |     |

|                                                         |                             | 64/32 MHz   | 5                   | 17.7  | 18.59      | 19.61 | 20.08 | 20.73 |     |

|                                                         |                             | 24/24 MHz   |                     | 12.15 | 12.97      | 13.93 | 14.39 | 15.04 |     |

|                                                         |                             | 12/12 MHz   |                     | 10.49 | 11.29      | 12.23 | 12.69 | 13.33 |     |

| XOSC+PLL,                                               |                             | 8/8 MHz     |                     | 7.812 | 8.57       | 9.471 | 9.925 | 10.56 |     |

| all modules clocks disabled;                            | $ m RI_{DD}$                | 64/32 MHz   |                     | 17.61 | 18.48      | 19.52 | 20.03 | 20.56 | mA  |

|                                                         |                             | 24/24 MHz   |                     | 12.06 | 12.86      | 13.84 | 14.35 | 14.88 |     |

|                                                         |                             | 12/12 MHz   | 3.3                 | 10.41 | 11.19      | 12.14 | 12.65 | 13.18 |     |

|                                                         |                             | 8/8 MHz     |                     | 7.726 | 8.47       | 9.388 | 9.878 | 10.41 |     |

| Stop mode ;HSI_8M                                       |                             | 8/8 MHz     | 5                   | 0.937 | 0.995      | 1.207 | 1.429 | 1.751 |     |

| (selectable inactive or active module keep active)      | $\mathrm{SI}_{\mathrm{DD}}$ | 8/8 MHz     | 3.3                 | 0.929 | 0.988      | 1.205 | 1.403 | 1.735 | mA  |

| Stop mode ;HSI_8M                                       | QT.                         | 8/8 MHz     | 5                   | 0.026 | 0.061      | 0.262 | 0.479 | 0.792 |     |

| (some selectable inactive or active module keep active) | $\mathrm{SI}_{\mathrm{DD}}$ | 8/8 MHz     | 3.3                 | 0.023 | 0.059      | 0.255 | 0.448 | 0.785 | mA  |

| Stop mode ;HSI_8M                                       | QI <sub>nn</sub>            | 8/8 MHz     | 5                   | 0.026 | 0.061      | 0.262 | 0.477 | 0.791 | m A |

| (selectable inactive or active module keep inactive)    | $\mathrm{SI}_{\mathrm{DD}}$ | 8/8 MHz     | 3.3                 | 0.023 | 0.06       | 0.254 | 0.447 | 0.786 | mA  |

|                                                         | $\mathrm{SI}_{\mathrm{DD}}$ | 32K         | 5                   | 0.016 | 0.027      | 0.083 | 0.145 | 0.242 | mA  |

| Standby mode(selectable inactive or active module keep active) |                             | 32K | 3.3 | 0.013 | 0.025 | 0.083 | 0.139 | 0.237 |    |

|----------------------------------------------------------------|-----------------------------|-----|-----|-------|-------|-------|-------|-------|----|

| Standby mode (selectable inactive or active module             | $\mathrm{SI}_{\mathrm{DD}}$ | 32K | 5   | 0.016 | 0.027 | 0.083 | 0.144 | 0.241 | A  |

| keep inactive)                                                 | SIDD                        | 32K | 3.3 | 0.013 | 0.024 | 0.082 | 0.139 | 0.237 | mA |

<sup>[1]</sup> 典型列里的数据在 25 °C  $V_{DD}=3.3/5$  V 条件下的统计值或是推荐值;

#### 6.2 动态规格

#### 6.2.1 控制时序

表 6-4 控制时序

| 编号 | C | 额定值                                       |                 | 符号                                               | 最小值                      | 典型值  | 最大值   | 单位           |

|----|---|-------------------------------------------|-----------------|--------------------------------------------------|--------------------------|------|-------|--------------|

|    |   |                                           |                 |                                                  |                          | [1]  |       |              |

| 1  | D | 系统和内核时钟(tsys                              | $= 1/f_{Sys}$ ) | $f_{\mathrm{Sys}}$                               | DC                       |      | 64    | MHz          |

| 2  | P | 总线频率(t <sub>cyc</sub> = 1/f <sub>Bu</sub> | s)              | $ m f_{Bus}$                                     | DC                       | _    | 32[2] | MHz          |

| 3  | P | 内部低功耗振荡器频                                 | [率              | $f_{ m LPO}$                                     | _                        | 32   | _     | kHz          |

| 4  | D | 外部复位脉冲宽度 [3                               | 8]              | $t_{ m extrst}$                                  | $1.5 \times t_{\rm sys}$ | _    | _     | s            |

| 5  | D | IRQ 脉冲宽度                                  | 运行模式            | t <sub>ILIH</sub> /                              | $1.5 \times t_{\rm sys}$ | _    | _     | s            |

|    |   |                                           | [4]             | $\mathbf{t}_{\scriptscriptstyle \mathrm{IHIL}}$  |                          |      |       |              |

|    | D |                                           | 停止模式            | t <sub>ILIH</sub> /                              | $1.5 \times t_{32k}$     | _    | _     | $\mathbf{s}$ |

|    |   |                                           | [4]             | $\mathbf{t}_{	ext{IHIL}}$                        |                          |      |       |              |

| 6  | D | 端口上升和下降时                                  | _               | $t_{ m Rise}$                                    | _                        | 10.2 | _     | ns           |

|    | D | 间- 标准驱动强度                                 |                 | $\mathbf{t}_{\scriptscriptstyle{\mathrm{Fall}}}$ | _                        | 9.5  | _     | ns           |

|    |   | (负载 = 50 pF) [5]                          |                 |                                                  |                          |      |       |              |

|    |   |                                           |                 |                                                  |                          |      |       |              |

|    | D | 端口上升和下降时                                  | _               | $t_{ m Rise}$                                    | _                        | 5.4  | _     | ns           |

|    | D | 间- 高驱动强度(负                                |                 | $t_{\scriptscriptstyle{\mathrm{Fall}}}$          | _                        | 4.6  | _     | ns           |

|    |   | 载 = 50 pF) [5]                            |                 |                                                  |                          |      |       |              |

<sup>[1]</sup> 除非另有说明, 否则典型值是指 VDD=5.0 V、25 °C 时的特性数据;

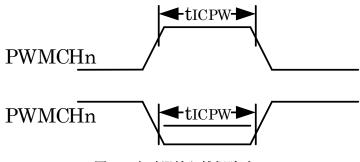

#### 6.2.2 PWM 模块时序

同步电路决定可识别的最短输入脉冲。这些同步电路的工作时钟被称作 PWM 时钟。

<sup>[2]</sup> AC7803x 系列产品的具体最大频率请参看选型手册;

<sup>[3]</sup> 这里保证可识别为 RESET\_B 引脚请求的最短脉冲;

<sup>[4]</sup> 这里保证可通过引脚同步电路的最短脉冲宽度。低于该宽度的脉冲有可能不被识别;

<sup>[5]</sup> 时序按 20%的  $V_{DD}$  电平和 80%的  $V_{DD}$  电平显示,温度范围-40 至 125 °C。

表 6-5 PWM 输入时序

| C | 功能       | 符号                       | 最小值 | 最大值  | 单位                  |

|---|----------|--------------------------|-----|------|---------------------|

| D | 定时器时钟频率  | $\mathbf{f}_{	ext{PWM}}$ | _   | 32 M | $_{ m Hz}$          |

| D | 输入捕捉脉冲宽度 | $t_{\rm ICPW}$           | 1.5 | _    | tPWM <sup>[1]</sup> |

[1] tPWM=1/ fPWM.

图 6-2 定时器输入捕捉脉冲

#### 6.3 热规格

#### 6.3.1 热特性

本节介绍有关工作温度范围、功耗和封装热阻的信息。I/O 引脚上的功耗通常比片上逻辑和电压调节器电路中的功耗少,且它由用户决定而并非由 MCU 设计控制。 要在功率计算中考虑 P<sub>I/O</sub>,请确定实际引脚电压和 Vss 或 VDD 之间的电压差并乘以 每个 I/O 引脚的引脚电流。除异常高引脚电流(高负载)外,引脚电压和 Vss 或 VDD之间的压差将会很小。

表 6-6 热学属性

| 电路板           | <i>/</i> // □     | 47.44           | 48    | 64    | * *  | 17/1.55- |

|---------------|-------------------|-----------------|-------|-------|------|----------|

| 类型            | 符号                | 描述              | LQFP  | LQFP  | 単位   | 附注       |

| 双层<br>(1s1p)  | $	heta_{ m JA}$   | 热阻,结到外部环境(自然对流) | 80.90 | 63.26 | °C/W | 1, 2     |

| 四 层<br>(2s2p) | $	heta_{ m JA}$   | 热阻,结到外部环境(自然对流) | 51.23 | 44.90 | °C/W | 1, 3     |

| 双层            | Өлма              | 热阻,结到外部环境(空气速率  | 49.87 | 49.00 | °C/W | 1, 3     |

| (1s1p)        |                   | 为200 英尺/分钟)     |       | 10.00 |      |          |

| 四层            | $\theta_{ m JMA}$ | 热阻,结到外部环境(空气速率  | 40.06 | 37.50 | °C/W | 1, 3     |

| (2s2p)        |                   | 为200 英尺/分钟)     |       | 37.50 |      |          |

| _             | $\theta_{ m JB}$  | 热阻,结到板          | 23.14 | 26.28 | °C/W | 4        |

| _             | θјс               | 热阻,结到管壳         | 15.88 | 11.82 | °C/W | 5        |

| 双层<br>(1s1p)  | $\Psi_{ m JT}$       | 热特性参数,结到外封装顶部中<br>心(自然对流) | 19.23 | 19.54 | °C/W | 6 |

|---------------|----------------------|---------------------------|-------|-------|------|---|

| 四 层<br>(2s2p) | $\Psi_{\mathrm{JT}}$ | 热特性参数,结到外封装顶部中<br>心(自然对流) | 20.17 | 19.78 | °C/W | 6 |

| 双层<br>(1s1p)  | $\Psi_{\mathrm{JB}}$ | 热特性参数,结到外封装底部中<br>心(自然对流) | 20.73 | 21.01 | °C/W | 7 |

| 四 层<br>(2s2p) | $\Psi_{\mathrm{JB}}$ | 热特性参数,结到外封装底部中<br>心(自然对流) | 21.76 | 21.83 | °C/W | 7 |

- 1. 结温是裸片大小、片上功耗、封装热阻、安装环境(板)温度、环境温度、气流、板上其他组件的功耗和 板热阻的函数。

- 2. 基于JEDEC JESD51-2 标准,在单层板(JESD51-3)水平方向。

- 3. 基于JEDEC JESD51-6,在电路板(JESD51-7)水平方向。

- 4. 裸片和印刷电路板上的热阻,基于JEDEC JESD51-8 标准。板温度在封装附近的板上表面测量。

- 5. 裸片和封装底部焊盘之间的热阻。忽略接触热阻。

- 6. 基于JEDEC JESD51-2 标准, 热特性参数表示封装顶部和结温度之间的温差。未提供希腊字母时的热特性。

- 7. 基于JEDEC JESD51-2 标准,热特性参数表示封装底部和结温度之间的温差。未提供希腊字母时的热特性。

可通过以下公式计算平均芯片结温 (TJ)(以°C 为单位):

$TJ = TA + (PD \times θ JA)$ , 其中:

TA = 环境温度,以°C 为单位;

θ JA = 封装热阻,结环境,以°C/W 为单位;

PD = Pint + PI/O

Pint = IDD × VDD, 以瓦特为单位 — 芯片内部功率;

PI/O = 输入和输出引脚上的功耗 — 由用户决定;

对于大多数应用, PI/O << Pint, 且可以忽略。PD 和 TJ (如果忽略 PI/O) 之间的近似 关系是:

$PD = K \div (TJ + 273 \text{ }^{\circ}C)$

求解以上等式中的 K:

$K = PD \times (TA + 273 \text{ °C}) + \theta \text{ JA} \times (PD)2$

其中 K 是特定部分的常数。

通过测量已知 TA 的 PD(处于均衡状态)来确定 K。使用此 K 值,可通过以上公式迭代求解任何 TA 值来获得 PD 和 TJ 值。

## 7 外设工作要求和行为

### 7.1 内核模块

### 7.1.1 SWD 电气规格

表 7-1 SWD 全电压范围电气规格

| 符号  | 说明                             | 最小值  | 最大值 | 单位  |

|-----|--------------------------------|------|-----|-----|

|     | 工作电压                           | 2.7  | 5.5 | V   |

| J1  | SWD_CLK 工作频率                   | 0    | 20  | MHz |

|     | • 串行线调试                        |      |     |     |

| J2  | SWD_CLK 周期                     | 1/J1 | _   | ns  |

| J3  | SWD_CLK 时钟脉宽                   | 20   | _   | ns  |

|     | • 串行线调试                        |      |     |     |

| J4  | SWD_CLK 上升和下降时间                | _    | 3   | ns  |

| J9  | 到 SWD_CLK 上升的 SWD_DIO 输入数据建立时间 | 5    | _   | ns  |

| *** |                                | _    |     |     |

| J10 | SWD_CLK 上升之后的 SWD_DIO 输入数据保持时间 | 5    | _   | ns  |

| J11 | SWD_CLK 高电平到 SWD_DIO 数据有效      | _    | 42  | ns  |

|     |                                |      |     |     |

## 7.2 外部振荡器 (OSC) 和内部时钟源(ICS) 特性

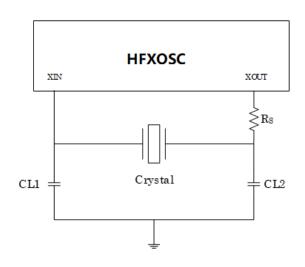

#### 7.2.1 外部高速振荡器(HFXOSC) 特性

表 7-2 XOSC 规格 (环境温度范围 = -40 至 125 °C)

| 编号 | C | 特性     | 符号   | 最小值  | 典型值 | 最大值 | 单位  |

|----|---|--------|------|------|-----|-----|-----|

| 1  | С | 振荡器频率  | fhi  | 8    | _   | 30  | MHz |

| 2  | D | 负载电容   | CL1, | 参见注释 | [1] | _   |     |

|    |   |        | CL2  |      |     |     |     |

| 3  | D | 串联电阻   | Rs   |      | 0   | _   | ΚΩ  |

| 4  | С | 晶振启动时间 | tcst |      |     | 2.5 | ms  |

[1] CL1 和 CL2 推荐使用为高频率应用设计、满足晶振需求的高质量外部陶瓷电容。CL1 和 CL2 通常大小相等。 在确定 CL1 和 CL2 的尺寸时,必须包含 PCB 和 MCU 引脚电容(10 pF 可作为引脚和电路板电容的粗略估计)。

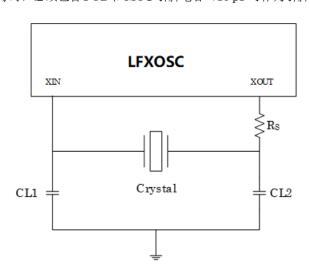

图 7-1 典型晶振或振荡器电路

表 7-3 XOSC 规格 (环境温度范围 = -40 至 125 °C)

#### 7.2.2 外部低速振荡器(LFXOSC) 特性

| 编号 | C | 特性    | 符号                      | 最小值 | 典型值    | 最大值 | 单位  |

|----|---|-------|-------------------------|-----|--------|-----|-----|

| 1  | C | 振荡器频率 | $\mathbf{f}_{	ext{hi}}$ | _   | 32.768 |     | KHz |

|   | 3m 7 |   | 10 11. | 10 3                    | - XX.1. IET | 天王山    | 取八區 | 十匹  |

|---|------|---|--------|-------------------------|-------------|--------|-----|-----|

| Ī | 1    | C | 振荡器频率  | $\mathbf{f}_{	ext{hi}}$ | _           | 32.768 | _   | KHz |

| I | 2    | D | 负载电容   | CL1,                    | 参见注释        | [1]    | _   |     |

|   |      |   |        | CL2                     |             |        |     |     |

|   | 3    | D | 串联电阻   | Rs                      |             | 0      |     | ΚΩ  |

|   | 4    | С | 晶振启动时间 | tcst                    | _           |        | 500 | ms  |

[1] CL1 和 CL2 推荐使用为高频率应用设计、满足晶振需求的高质量外部陶瓷电容。CL1 和 CL2 通常大小相等。 在确定 CL1 和 CL2 的尺寸时,必须包含 PCB 和 MCU 引脚电容( $10\,pF$  可作为引脚和电路板电容的粗略估计)。

图 7-2 典型晶振或振荡器电路

#### 7.2.3 内部 RC 特性

#### 表 7-4 OSC 和 ICS 规格 (环境温度范围 = -40 至 125 °C)

| 编号 | C | 特性                               |                                    | 符号                   | 最小值   | 典型值 | 最大值   | 単位  |

|----|---|----------------------------------|------------------------------------|----------------------|-------|-----|-------|-----|

| 1  | P | LFOSC 输出频率范围                     | 温度范围:                              | $f_{ m lfosc}$       | 7.736 | 8   | 8.264 | MHz |

|    |   |                                  | -40 °C 至 125°C                     |                      |       |     |       |     |

| 2  | P | LFOSC 在 T = 25 °C,               | 温度范围:                              | $\Delta f_{int\_t}$  | -3.3  |     | 3.3   | %   |

|    |   | V <sub>DD</sub> = 2.7~5.5 V 的条件下 | -40 °C 到 125°C                     |                      |       |     |       |     |

| 3  | P | LPOSC 内部基准时钟频                    | T = 25 °C,                         | $f_{int\_ft}$        | _     | 32  | _     | KHz |

|    |   | 率,出厂已调整                          | $V_{\rm DD} = 5 \text{ V}$         |                      |       |     |       |     |

| 4  | P | LPOSC 出厂已调整的内                    | 温度范围:                              | $\Delta f_{int\_ft}$ | -10   | _   | 10    | %   |

|    |   | 部振荡器精度                           | -40 °C 到 125°C,                    |                      |       |     |       |     |

|    |   |                                  | $V_{\mathrm{DD}} = 5 \mathrm{\ V}$ |                      |       |     |       |     |

|    |   |                                  |                                    |                      |       |     |       |     |

#### 7.2.4 PLL 特性

#### 表 7-5 PLL 特性

| 编号 | 符号                   | 参数         | 最小值 | 典型值 | 最大值  | 单位  |

|----|----------------------|------------|-----|-----|------|-----|

| 1  | f <sub>PLL_IN</sub>  | PLL 输入时钟频率 | 4   | _   | 48   | MHz |

| 2  | fPLL_REF             | PLL 参考时钟频率 | _   | _   | 12   | MHz |

| 3  | fpll_out             | PLL 输出时钟频率 | 8   | _   | 192  | MHz |

| 4  | f <sub>VCO_OUT</sub> | VCO 输出频率   | 400 | _   | 1000 | MHz |

工作环境温度: -40~125°C

f<sub>PLL\_OUT</sub> = f<sub>VCO\_OUT</sub> /Postdiv, Postdiv 可以为 2,4,6,...,60,62

f<sub>PLL\_REF</sub> = f<sub>PLL\_IN</sub> /Prediv, Prediv 可以为 1,2,4

## 7.3 片内 Flash 规格

本节详细介绍了片内 Flash 存储器的编程/擦除时间和编程/擦除次数。

### 表 7-6 片内 Flash 特性

| C | 特性                      | 符号                  | 最小值 | 典型值 | 最大值 | 单位  |

|---|-------------------------|---------------------|-----|-----|-----|-----|

| D | - 40°C 到 125°C 温度环境下编程/ | $V_{ m prog/erase}$ | 2.7 | _   | 5.5 | V   |

|   | 擦除工作电压                  |                     |     |     |     |     |

| D | 读取操作的供电电压               | $V_{\mathrm{Read}}$ | 2.7 | _   | 5.5 | V   |

| D | 片内 Flash 总线频率           | fsys                | 8   | 32  | 64  | MHz |

# autochips

| D | 片内 Flash 读取一次时间                                            | trdonce | 4                             | 4      | 6 | $t_{\rm cyc}$ [1]    |

|---|------------------------------------------------------------|---------|-------------------------------|--------|---|----------------------|

| D | 批量擦除(所有主块页)                                                | tmer    | _                             | 12     | _ | ms                   |

| D | 页擦除(一页)                                                    | tper    | _                             | 5      | _ | ms                   |

| D | 批量擦除校验                                                     | tmerv   | _                             | 131081 | _ | t <sub>cyc[1]</sub>  |

| D | 页擦除校验                                                      | tperv   | _                             | 521    | _ | t <sub>cyc</sub> [1] |

| D | 编程片内 Flash (1 个字)                                          | tprg1   | _                             | 35     | _ | us                   |

| D | 编程片内 Flash (n 个字, n>1)                                     | tPRGn   | _                             | 35×n   | _ | us                   |

| С | 片内 Flash 寿命(擦除-编程循环次<br>数)T <sub>A</sub> = -40 °C 至 125 °C | nedr    | 10 k                          | _      | _ | 次                    |

| С | 数据保持时间                                                     | tret    | 100@25℃<br>20@105℃<br>10@125℃ | _      | _ | 年                    |

<sup>[1]</sup>  $t_{cyc}$  = 1/  $f_{sys\,\circ}$

## 7.4 模拟

#### 7.4.1 ADC 特性

表 7-7 12 位 ADC 和温度传感器工作条件和特性

| C | 符号                    | 参数           | 条件                          | 最小值 | 典型值  | 最大值               | 单位  |

|---|-----------------------|--------------|-----------------------------|-----|------|-------------------|-----|

| D | V <sub>AVDD</sub>     | 供电电压         | 绝对值                         | 2.7 | _    | 5.5               | V   |

| D | V <sub>REFH</sub> [1] | 正参考输入        | 绝对值                         | 2.9 | _    | V <sub>AVDD</sub> | V   |

| D | VREFL                 | 负参考输入        | 绝对值                         | _   | 0    | _                 | V   |

| D | $V_{\mathrm{IN}}$     | 输入电压范围       | 电源作为参 考                     | 0   | _    | $V_{ m AVDD}$     | v   |

| D | VIN                   | 柳八七匹花四       | 外部 VREFH<br>为参考             | 0   |      | Vrefh             | v   |

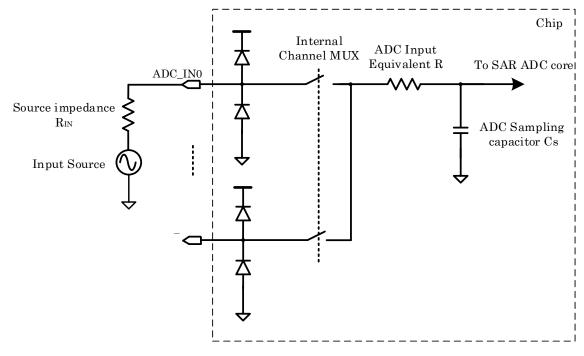

| D | $ m R_{IN}$           | 输入源阻抗        | 参考公式[2]                     | _   | _    | _                 | Ω   |

| D | Cadc                  | 内部采样电容       | _                           | _   | 2.02 | _                 | pF  |

| D | Radc                  | 采样开关电阻       | _                           | _   | 2.5  | _                 | ΚΩ  |

| D | fadc                  | ADC 时钟频<br>率 | _                           | _   | _    | 16                | MHz |

| D | N <sub>sample</sub>   | 采样周期数        |                             | _   | 8    | _                 |     |

| С | $f_{ m trig}$         | 采样频率         | f <sub>ADC</sub> =16<br>MHz | _   | _    | 0.8               | MHz |

| C | 符号  | 参数     | 条件 | 最小值 | 典型值       | 最大值 | 单位      |

|---|-----|--------|----|-----|-----------|-----|---------|

| С | INL | 积分非线性  | _  | _   | $\pm 1.5$ |     | LSB [3] |

| С | DNL | 差分非线性  | _  | _   | $\pm 1.5$ | _   | LSB [3] |

| С | TUE | 总不可调误差 | _  | -8  | _         | 8   | LSB [3] |

| Р | СН  | 外部通道   | _  |     | _         | 19  | _       |

- [1] 采用 VREFH 时,需要 AVDD≥VREFH

- [2] 输入源阻抗与采样时间关系需满足下式:  $R_{IN} < \frac{N_{sample}}{f_{ADC}*C_{ADC}*ln(2^{N+2})} R_{ADC}$ ,式中 N 为 ADC 的位数,ADC 采样时长需满足 0.25LSB 的建立精度,式中未考虑 PAD 端的寄生电容。

- [3] 当以电源作为 ADC 参考 LSB =  $V_{AVDD}$  /2<sup>12</sup>,当以  $V_{REFH}$  作为 ADC 参考,LSB =  $V_{REFH}$  /2<sup>12</sup>。

表 7-8 12 位 ADC 和温度传感器工作条件和特性 (续)

| 特性      | 条件            | C | 符号      | 最小值 | 典型值   | 最大值 | 单位    |

|---------|---------------|---|---------|-----|-------|-----|-------|

| 温度传感器斜率 | -40 °C~125 °C | D | Slope   | _   | 2.6   | _   | mV/°C |

| 温度传感器电压 | 25 °C         | D | VTEMP25 | _   | 0.816 | _   | V     |

图 7-2 ADC 输入等效图

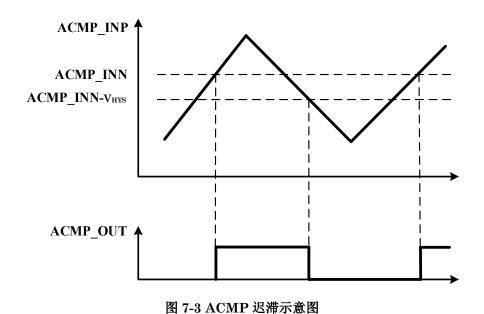

#### 7.4.2 模拟比较器 (ACMP) 和数模转换器电气规格

表 7-9 比较器电气规格

| C | 特性                      | 条件                     | 符号                 | 最小值          | 典型值  | 最大值                    | 单位  |

|---|-------------------------|------------------------|--------------------|--------------|------|------------------------|-----|

| D | 供电电压                    | _                      | V <sub>AVDD</sub>  | 2.7          | _    | 5.5                    | V   |

| T | 供电电流 (工作模式)             | 仅 ACMP                 | $I_{DDA}$          | _            | _    | 25                     | μA  |

| D | 模拟输入电压                  | _                      | $V_{AIN}$          | $V_{\rm SS}$ | _    | $V_{AVDD}$             | V   |

| P | 模拟输入失调电压 <sup>[2]</sup> | _                      | VAIO               | -30          | _    | 30                     | mV  |

| С | 模拟比较器迟滞电压[2]            | 无迟滞                    | V <sub>HYS</sub>   | _            | 0    | _                      | mV  |

| С | 模拟比较器迟滞电压[2]            | 低迟滞                    | V <sub>HYS</sub>   | _            | 10   | _                      | mV  |

| С | 模拟比较器迟滞电压[2]            | 中等迟滞                   | $V_{\mathrm{HYS}}$ | _            | 20   | _                      | mV  |

| С | 模拟比较器迟滞电压[2]            | 高迟滞                    | $V_{\mathrm{HYS}}$ | _            | 40   | _                      | mV  |

| D | 供电电流 (关闭模式)             | _                      | Iddaoff            | _            | _    | 100                    | nA  |

| T | 传播延迟[2]                 | _                      | ${ m t_D}$         | _            | 0.4  | 1[1]                   | μs  |

| P | 数模转换器积分非线性[3]           | Vref=V <sub>AVDD</sub> | INL                | -1           | _    | 1                      | LSB |

| P | 数模转换器积分非线性[3]           | Vref=V <sub>BG</sub>   | INL                | -1           | _    | 1                      | LSB |

| T | 数模转换器输出                 | 带缓冲器                   | DAC_OUT            | 0.2          | _    | V <sub>AVDD</sub> -0.2 | V   |

| T | 数模转换器输出                 | 不带缓冲器                  | DAC_OUT            | 0.2          | _    | V <sub>AVDD</sub> -0.2 | V   |

| D | 数模转换器负载电容               | _                      | $C_{LOAD}$         | _            | _    | 6                      | pF  |

| D | 数模转换器静态功耗               | Vref=5.5V              | Idda               | _            | 48.3 | _                      | μА  |

| D | 数模转换器静态功耗               | Vref=V <sub>BG</sub>   | $I_{DDA}$          | _            | 48.5 | _                      | μΑ  |

[1] ACMP 输入端接外部通道,滤波档位选择 bypass。

[2]该测试环境在输入电压=VAVDD /2 时。

[3]带缓冲器。

杰发科技机密文件

## 7.5 通信接口

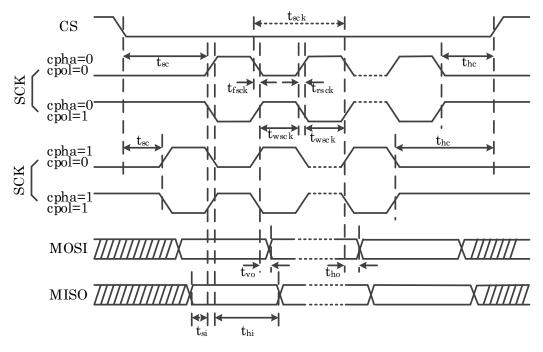

#### 7.5.1 SPI 规格

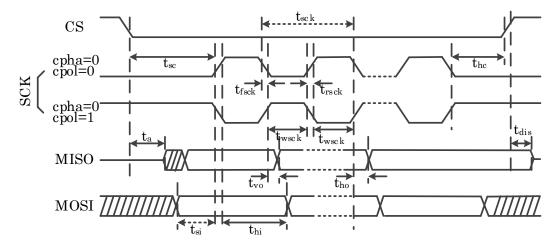

串行外设接口(SPI)可为主从操作提供同步串行总线。用户可以自由配置多项传输参数。下面各表将介绍经典 SPI 时序模式的时序特性。有关修正传输格式的信息,请参见本芯片"参考手册"中的 SPI 一章。这些格式主要用于和速度较慢的外围设备通信。

图 7-4 SPI 时序图 —主机

表 7-10 SPI 特性 - 主机

| 符号                         | 说明                    | 最小值                   | 最大值                  | 单位 | 注解                                                            |

|----------------------------|-----------------------|-----------------------|----------------------|----|---------------------------------------------------------------|

| $\mathbf{f}_{\mathrm{op}}$ | 操作频率                  | f <sub>bus</sub> /512 | 12M                  | Hz | f <sub>bus</sub> 是总线时钟,最高 32Mhz,最大操作频率可为 f <sub>bus</sub> 二分频 |

| $\mathbf{t_{sc}}$          | CS 建立时间               | 1×t <sub>bus</sub>    | 256×t <sub>bus</sub> | ns | 从 CS 下降沿到第一个 SCK 边沿的时间                                        |

| the                        | CS 保持时间               | 1×t <sub>bus</sub>    | 256×t <sub>bus</sub> | ns | 从最后一个 SCK 边沿到 CS 上升沿的时间                                       |

| $\mathbf{t}_{	ext{wsck}}$  | 时钟(SCK) 高电平或<br>低电平时间 | 1×t <sub>bus</sub>    | 256×t <sub>bus</sub> | ns | 未考虑 trsck和 tfsck                                              |

| $\mathbf{t_{si}}$          | 数据输入建立时间              | 10                    | _                    | ns | _                                                             |

| 符号                | 说明       | 最小值 | 最大值 | 单位 | 注解 |

|-------------------|----------|-----|-----|----|----|

| $\mathbf{t_{hi}}$ | 数据输入保持时间 | 10  | _   | ns | _  |

| $\mathbf{t_{vo}}$ | 数据输出有效时间 | _   | 15  | ns | _  |

| $\mathbf{t_{ho}}$ | 数据输出保持时间 | -2  | _   | ns | _  |

图 7-5 SPI 时序图 -从机(cpha=0)

图 7-6 SPI 时序图 -从机(cpha=1)

表 7-11 SPI 特性 - 从机

| 符号                         | 说明           | 最小值                       | 最大值  | 单位 | 注解                      |

|----------------------------|--------------|---------------------------|------|----|-------------------------|

| fop                        | 操作频率         | _                         | 12 M | Hz | 轮询接收方式,最高 12M;          |

| $\mathbf{t}_{\mathrm{sc}}$ | CS 建立时间      | 2×t <sub>bus</sub>        |      | ns | 从 CS 下降沿到第一个 SCK 边沿的时间  |

| $\mathbf{t_{hc}}$          | CS 保持时间      | $2 \times t_{\text{bus}}$ |      | ns | 从最后一个 SCK 边沿到 CS 上升沿的时间 |

| $\mathbf{t_a}$             | 从机访问时间       | _                         | 65   | ns | 从高阻态到数据有效的时间            |

| $\mathbf{t_{dis}}$         | 从机 MISO 禁用时间 | _                         | 65   | ns | 到高阻态状态的保持时间             |

| 符号                | 说明       | 最小值 | 最大值 | 单位 | 注解 |

|-------------------|----------|-----|-----|----|----|

| $\mathbf{t_{si}}$ | 数据输入建立时间 | 40  | _   | ns | _  |

| $\mathbf{t_{hi}}$ | 数据输入保持时间 | 20  | _   | ns | _  |

| $t_{ m vo}$       | 数据输出有效时间 | _   | 40  | ns | _  |

| $t_{ m ho}$       | 数据输出保持时间 | 22  | _   | ns | _  |

#### 7.5.2 UART 规格

通用的异步收发器(UART)的基本功能是按单 bit 传输和接收串行数据。在 AC7803x 芯片中,额外加入了软件 LIN 功能,用来实现间断区域,同步区域以及数据的传输。下面将介绍 UART 主要的参数特性:

- 1. 最多支持 3 路 UART, 3 路 UART 都支持软 LIN 功能(同一个 UART 的 UART 功能和 LIN 功能不能同时使用);

- 2. UART 支持产生或接收波特率范围在 600 bps~4.2Mbps;

- 3. GPIO 管脚中断脉冲宽度最小应超过 333 ns。由于管脚对输入信号没有经过无源滤波处理,因此至少要保证超过此脉冲宽度,才能保证输入信号可以被识别;

- 4. 使用软件 LIN 功能时可支持的最高波特率为 20 Kbps;

- 5. 使用软件 LIN 功能时,可选择开启自动波特率检测。此时接收波特率可容忍的误差范围是-50%~+100%。

#### 7.5.3 CAN 规格

#### 表 7-12 CAN 唤醒脉冲特性

| 参数                   | 符号   | 最小值 | 典型值 | 最大值  | 单位 |

|----------------------|------|-----|-----|------|----|

| 过滤掉的 CAN "显性" 唤醒脉冲参数 | twup | 1.4 |     | 3.45 | μs |

| 有效的 CAN"显性"唤醒脉冲参数    | twup | _   | 2   | _    | μs |

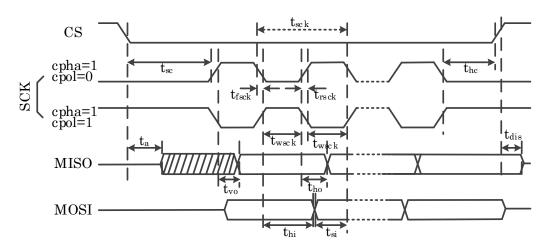

#### 7.5.4 I2C 规格

#### 表 7-13 不同模式下 I2C 总线特性

| 符号                           | 参数          | 标准模式 |     | 快速模式 |     | 快速+模式 |      | 单位  |

|------------------------------|-------------|------|-----|------|-----|-------|------|-----|

|                              |             | 最小值  | 最大值 | 最小值  | 最大值 | 最小值   | 最大值  |     |

| $\mathbf{f}_{\mathrm{SCL}}$  | SCL 时钟频率    | 0    | 100 | 0    | 400 | 0     | 1000 | KHz |

| $\mathbf{t}_{	ext{HD}}$ ;STA | 开始状态保持时间    | 4    | _   | 0.6  | _   | 0.26  | _    | μs  |

| $\mathbf{t}_{	ext{LOW}}$     | SCL 时钟低电平长度 | 4.7  | _   | 1.3  | _   | 0.5   | _    | μs  |

| thigh                | SCL 时钟高电平长度           | 4                    | _    | 0.6                                  | _   | 0.26                                 | _    | μs |

|----------------------|-----------------------|----------------------|------|--------------------------------------|-----|--------------------------------------|------|----|

| tsu;sta              | 重复开始状态建立时间            | 4.7                  | _    | 0.6                                  | _   | 0.26                                 | _    | μs |

| t <sub>HD</sub> ;DAT | 数据保持时间                | 0                    | _    | 0                                    | _   | 0                                    | _    | μs |

| t <sub>SU</sub> ;DAT | 数据建立时间                | 250                  | _    | 100                                  | _   | 50                                   | _    | ns |

| $\mathbf{t_r}$       | SDA 和 SCL 信号的上升<br>时间 | _                    | 1000 | 20                                   | 300 | -                                    | 120  | ns |

| tf                   | SDA和 SCL 信号的下降<br>时间  | _                    | 300  | 20 ×<br>(V <sub>DD</sub> /<br>5.5 V) | 300 | 20 ×<br>(V <sub>DD</sub> /<br>5.5 V) | 120  | ns |

| tsu;sto              | 结束状态的建立时间             | 4                    | _    | 0.6                                  | _   | 0.26                                 | _    | μs |

| tBUF                 | 结束和开始状态之间的总<br>线空闲时间  | 4.7                  | _    | 1.3                                  | _   | 0.5                                  | _    | μs |

| Сь                   | 总线负载电容                | _                    | 400  | _                                    | 400 | _                                    | 550  | рF |

| tvd;dat              | 数据有效时间                | _                    | 3.45 | _                                    | 0.9 | _                                    | 0.45 | μs |

| tvd;ACK              | 应答数据有效时间              | _                    | 3.45 | _                                    | 0.9 | _                                    | 0.45 | μs |

| V <sub>nL</sub>      | 低电平期间的噪声              | $0.1V_{\mathrm{DD}}$ | _    | $0.1 V_{\mathrm{DD}}$                | _   | $0.1 V_{\mathrm{DD}}$                | _    | V  |

| V <sub>nH</sub>      | 高电平期间的噪声              | $0.2 V_{ m DD}$      | _    | $0.2 V_{ m DD}$                      | _   | $0.2 V_{ m DD}$                      | _    | V  |

# autochips

图 7-7 标准与快速模式下 I2C 总线时序图

#### 7.5.5 EIO 规格

EIO (Enhanced IO) 是一个高度可配置的模块,提供了广泛的功能,包括:

- 模拟各种串行通信协议

- 4 个灵活的 16 位定时器,支持各种触发、复位、启用和禁用条件

- 4 个可配置的 32 位移位器,支持发送、接收和匹配存储功能

凭借 4 个定时器和 4 个移位器, EIO 模块能够支持广泛的协议, 包括但不限于:

- UART 发送和接收

- I2C 主机

- SPI 主机和从机

- I2S 主机和从机

- PWM 波形生成

# autochips

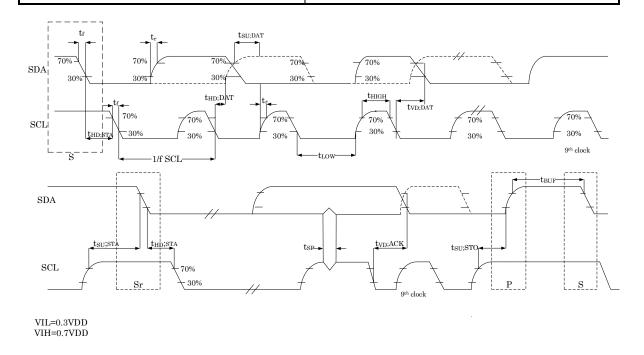

#### 尺寸 8

#### LQFP48 封装信息 8.1

图 8-1 LQFP - 48 引脚, 7 x 7 毫米薄行低轮廓四方引脚扁平式封装外形 [1]

[1] 该图绘制比例和实物比例有差别。

表 8-1 LQFP - 48 引脚, 7 x 7 毫米薄行低轮廓四方引脚扁平式封装外形机械数据 [1]

| 数据项                 |   | 符号 | 最小值   | 标准值           | 最大值   |  |

|---------------------|---|----|-------|---------------|-------|--|

| 总高度                 |   | A  | _     | _             | 1.60  |  |

| 站立高度                |   | A1 | 0.05  |               | 0.15  |  |

| 模塑厚度                |   | A2 | 1.35  | 1.40          | 1.45  |  |

| 框架到模塑体厚度            |   | A3 | 0.59  | 0.64          | 0.69  |  |

| 引脚宽度                |   | b  | 0.18  | _             | 0.27  |  |

| 引脚基材宽度              |   | b1 | 0.17  | 0.20          | 0.23  |  |

| 引脚厚度                |   | c  | 0.13  | _             | 0.18  |  |

| 引脚基材厚度              |   | c1 | 0.117 | 0.127         | 0.137 |  |

| 外引脚封装体尺寸            | X | D  | 8.80  | 9.00          | 9.20  |  |

| / JIMEST 70 (平) ( ) | Y | Е  | 8.80  | 9.00          | 9.20  |  |

| 封装体尺寸               | X | D1 | 6.90  | 7.00          | 7.10  |  |

| 五秋叶/C1              | Y | E1 | 6.90  | 7.00          | 7.10  |  |

| 引脚间距                |   | e  | 0.40  | 0.40 0.50     |       |  |

| Н                   |   | Н  | 8.14  | 8.17          | 8.20  |  |

| L                   |   | L  | 0.50  | 50 —          |       |  |

| 引脚长度                |   | L1 |       | 1.00REF       |       |  |

| 引脚圆弧半径              |   | R1 | 0.08  | _             | _     |  |

| R2                  |   | R2 | 0.08  |               | 0.20  |  |

| θ                   |   | θ  | 0°    | $3.5^{\circ}$ | 7°    |  |

| θ1                  |   | θ1 | 11°   | 12°           | 13°   |  |

| θ2                  |   | θ2 | 11°   | 12°           | 13°   |  |

<sup>[1]</sup> 尺寸以毫米表示和度量。

#### LQFP48产品正印:

下图给出了顶部正印方向与引脚1标识符位置的示例。

# autochips

图 8-2 LQFP48 正印示例 (封装顶视图)

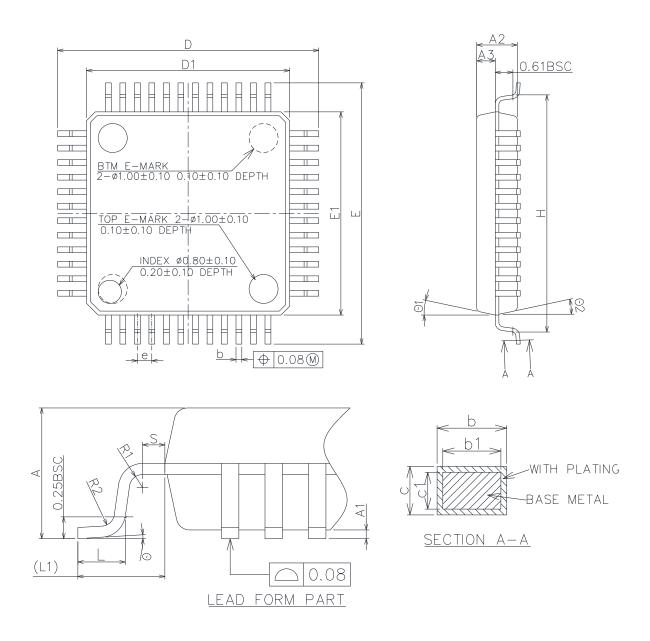

## 8.2 LQFP64 封装信息

图 8-3 LQFP - 64 引脚, 10 x 10 毫米薄行低轮廓四方引脚扁平式封装外形 [1]

[1] 该图绘制比例和实物比例有差别。

#### 表 8-2 LQFP - 64 引脚, 10 x 10 毫米薄行低轮廓四方引脚扁平式封装外形机械数据 [1]

| 数据项       |   | 符号 | 最小值         | 标准值           | 最大值   |  |  |

|-----------|---|----|-------------|---------------|-------|--|--|

| 总高度       |   | A  |             |               | 1.60  |  |  |

| 站立高度      |   | A1 | 0.05 —      |               | 0.15  |  |  |

| 模塑厚度      |   | A2 | 1.35        | 1.35 1.40     |       |  |  |

| 框架到模塑体厚度  |   | A3 | 0.59        | 0.64          | 0.69  |  |  |

| 引脚宽度      |   | b  | 0.18        | _             | 0.27  |  |  |

| 引脚基材宽度    |   | b1 | 0.17        | 0.20          | 0.23  |  |  |

| 引脚厚度      |   | c  | 0.13        | _             | 0.18  |  |  |

| 引脚基材厚度    |   | c1 | 0.117       | 0.117 0.127   |       |  |  |

| 外引脚封装体尺寸  | X | D  | 11.95       | 12.00         | 12.05 |  |  |

| 7 分解的农种人的 | Y | Е  | 11.95       | 12.00         | 12.05 |  |  |

| 封装体尺寸     | X | D1 | 9.90        | 10.00         | 10.10 |  |  |

| 五秋件/C1    | Y | E1 | 9.90        | 10.00         | 10.10 |  |  |

| 引脚间距      |   | e  | 0.40 0.50   |               | 0.60  |  |  |

| Н         |   | Н  | 11.09 11.13 |               | 11.17 |  |  |

| L         |   | L  | 0.53        | 0.70          |       |  |  |

| 引脚长度      |   | L1 | 1.00REF     |               |       |  |  |

| 引脚圆弧半径    |   | R1 | 0.15REF     |               |       |  |  |

| R2        |   | R2 |             | 0.13REF       |       |  |  |

| θ         |   | θ  | 0°          | $3.5^{\circ}$ | 7°    |  |  |

| θ1        |   | θ1 | 0°          |               | _     |  |  |

| θ2        |   | θ2 | 11°         | 12°           | 13°   |  |  |

| θ3        |   | θ3 | 11°         | 12°           | 13°   |  |  |

<sup>[1]</sup> 尺寸以毫米表示和度量。

#### LQFP64产品正印:

下图给出了顶部正印方向与引脚 1 标识符位置的示例。

# autochips

图 8-4 LQFP64 正印示例 (封装顶视图)

39/43

## 9 引脚分配

## 9.1 信号多路复用和引脚分配

下表显示的是各引脚上的信号以及这些引脚在本文档支持的器件上的位置。"端口控制模块"负责选择每个引脚上的 ALT 功能。

表 9-1 信号多路复用和引脚分配表

| 48  | 64          | A G=000       |              |            |                          |            |              |                  |            |

|-----|-------------|---------------|--------------|------------|--------------------------|------------|--------------|------------------|------------|

| PIN | PIN<br>LQFP | AC7803<br>PAD | Function 0   | Function 1 | Function 2               | Function 3 | Function 4   | Function 5       | Function 6 |

| 1   | 1           | PB11          | GPIO         | PWM0_CH3   | SPI1_MISO                | SPI1_MOSI  | PWM2_CH1     | EIO_D1           | HIGH_Z     |

| 2   | 2           | PB12          | GPIO         | PWM0_CH2   |                          | SPI1_SCK   | PWM2_CH0     | EIO_D0           | HIGH_Z     |

|     | 3           | PC10          | GPIO         | SPI1_NSS   | Timer_ALT0               | PWM1_CH5   |              | EIO_D5           | HIGH_Z     |

|     | 4           | PC11          | GPIO         | CLKOUT     |                          | PWM1_CH4   | CAN0_STDBY   | EIO_D4           | HIGH_Z     |

| 3   | 5           | PB0           | GPIO         | CAN0_TX    | PWM2_CH3                 | SPI1_MISO  | OSC32_IN*AN  | EIO_D7           | HIGH_Z     |

| 4   | 6           | PB1           | GPIO         | CAN0_RX    | PWM2_CH2                 | SPI1_NSS   | OSC32_OUT*AN | EIO_D6           | HIGH_Z     |

| 5   | 7           | VDD1          |              |            |                          |            |              |                  |            |

| 6   | 8           | VDDA          |              |            |                          |            |              |                  |            |

|     | 9           | VREF+         |              |            |                          |            |              |                  |            |

| 7   | 10          | VSS1          |              |            |                          |            |              |                  |            |

| 8   | 11          | PA12          | GPIO         | I2C0_SCL   | OSC_IN <sup>[1]</sup>    | PWM0_FLT0  |              |                  | HIGH_Z     |

| 9   | 12          | PA15          | GPIO         | I2C0_SDA   | OSC_OUT <sup>[1]</sup>   | PWDT0_IN0  |              |                  | HIGH_Z     |

|     | 13          | PC12          | GPIO         | PWM0_FLT0  | UART2_RTS                | PWM2_FLT0  |              | ACMP_OUT         | HIGH_Z     |

| 10  | 14          | PA0           | GPIO         | PWM0_CH1   | UARTO_RTS                | I2C0_SCL   | SPI0_MISO    | VREF-            | HIGH_Z     |

| 11  | 15          | PA1           | GPIO         | PWM0_CH0   | UARTO_CTS                | I2C0_SDA   | SPI0_SCK     | VREF+            | HIGH_Z     |

| 12  | 16          | PB13          | GPIO         | PWM2_CH3   | UART2_CTS                | I2C1_SCL   |              |                  | HIGH_Z     |

| 13  | 17          | PB3           | GPIO         | PWM2_CH2   | PWM1_CH7                 | SPI0_MOSI  | CAN1_STDBY   | ACMP_IN8[1]      | HIGH_Z     |

| 14  | 18          | PA2           | GPIO         | PWM2_CH1   | ADC_IN8[1]               | SPI0_MISO  | SPI0_NSS     | CLKOUT           | HIGH_Z     |

| 15  | 19          | PA3           | GPIO         | PWM2_CH0   | ADC_IN7[1]               | SPI0_SCK   | SPI0_MOSI    | DAC_OUT          | HIGH_Z     |

| 16  | 20          | PA4           | GPIO         | PWM0_CH3   | ADC_IN6/ACMP_IN6[1]      | UART1_TX   | CAN1_TX      | UARTO_TX         | HIGH_Z     |

| 17  | 21          | PA5           | GPIO         | PWM0_CH2   | ADC_IN5/ACMP_IN5[1]      | UART1_RX   | CAN1_RX      | UARTO_RX         | HIGH_Z     |

|     | 22          | PC13          | GPIO         | UART2_TX   | ACMP_IN10 <sup>[1]</sup> | PWM0_FLT0  |              |                  | HIGH_Z     |

|     | 23          | PC14          | GPIO         | UART2_RX   | ACMP_IN11 <sup>[1]</sup> | PWM2_FLT0  |              |                  | HIGH_Z     |

| 18  | 24          | PA6           | GPIO         | BOOT[1]    | Timer_ALT1               | SPI0_NSS   | PWM2_CH3     | PWM2_FLT0        | HIGH_Z     |

| 19  | 25          | PB14          | GPIO         | PWM0_CH1   | ADC_IN15[1]              | SPI1_MOSI  |              | PWM1_CH7         | HIGH_Z     |

|     | 26          | PC15          | GPIO         | PWM0_CH0   | ADC_IN16 <sup>[1]</sup>  | SPI1_MISO  |              | PWM1_CH6         | HIGH_Z     |

|     | 27          | PD0           | GPIO         | PWM1_FLT1  | ADC_IN17[1]              |            | CAN1_TX      | UART2_TX         | HIGH_Z     |

| 20  | 28          | PB15          | GPIO         | PWM1_FLT0  | ADC_IN11[1]              | SPI1_SCK   | CAN1_RX      | UART2_RX         | HIGH_Z     |

| 21  | 29          | PC0           | GPIO         | PWM1_CH3   | ADC_IN12[1]              | SPI1_MISO  | SPI1_SCK     | CAN1_STDBY       | HIGH_Z     |

| 22  | 30          | PC1           | GPIO         | PWM1_CH2   | ADC_IN13[1]              | SPI1_NSS   |              |                  | HIGH_Z     |

| 23  | 31          | PB4           | GPIO         | PWM1_CH1   | ADC_IN9[1]               | SPI0_MISO  | PWM0_CH0     | PWM2_CH2         | HIGH_Z     |

| 24  | 32          | PB5           | GPIO         | PWM1_CH0   | ADC_IN10[1]              | SPI0_SCK   | PWM0_CH1     | CAN0_STDBY       | HIGH_Z     |

| 25  | 33          | PA7           | GPIO         | UARTO_TX   | ADC_IN4/ACMP_IN4[1]      | SPI0_MOSI  | CAN0_TX      | PWM1_CH5         | HIGH_Z     |

|     | 34          | PA8           | GPIO         | UARTO_RX   | ADC_IN3/ACMP_IN3[1]      | SPI0_NSS   | CANO_RX      | Timer_ALT2       | HIGH_Z     |

| 27  | 35          |               | GPIO         | UART1_TX   | PWM2_FLT0                | UARTO_TX   | PWM1_CH0     | UARTO_RTS        | HIGH_Z     |

| 28  |             |               | GPIO         | UART1_RX   | PWM1_FLT1                | UARTO_RX   | PWM1_CH1     | UARTO_CTS        | HIGH_Z     |

|     | 37          | PA9           | GPIO         | PWM2_FLT0  | ADC_IN2/ACMP_IN2[1]      | RTC_CLKIN  | UART1_RTS    | PWM1_CH3         | HIGH_Z     |

|     | 38          |               | GPIO         | PWM0_FLT0  | ADC_IN18[1]              | SPI1_NSS   | UART1_CTS    | PWM1_CH5         | HIGH_Z     |

|     | 39          |               | GPIO         | PWM1_CH7   | PWM1_FLT0                |            |              |                  | HIGH_Z     |

| 30  | 40          | VSS2          |              |            |                          |            |              |                  |            |

|     | 41          | VDD2          |              |            |                          |            |              |                  |            |

| 32  | 42          |               | GPIO         | PWM0_CH1   | ADC_IN14[1]              | I2C1_SDA   | CAN1_TX      | PWM1_FLT1        | HIGH_Z     |

| -   | 43          |               | GPIO         | PWM0_CH0   | PWM1_FLT0                |            | CAN1_RX      |                  | HIGH_Z     |

|     | 44          |               | GPIO         | PWM0_FLT0  | PWM1_FLT1                |            | CAN1_STDBY   |                  | HIGH_Z     |

| 33  | 45          |               | GPIO         | PWM1_CH6   | PWM1_FLT0                | CAN0_STDBY | SPI1_NSS     | EIO_D7           | HIGH_Z     |

| 34  |             |               | GPIO         | PWM1_CH6   | PWDT0_IN1                | SPIO_NSS   | SPI1_MOSI    | EIO_D6           | HIGH_Z     |

| 35  | 47          |               | GPIO         | PWM1_CH3   | ACMP_IN7[1]              | I2C0_SCL   | UARTO_TX     | EIO_D5           | HIGH_Z     |

| 36  | 48          |               | GPIO<br>GPIO | _          | +                        |            | UARTO_RX     | EIO_D3<br>EIO_D4 | HIGH_Z     |

| აღ  | 40          | r Dð          | GLIO         | PWM1_CH2   | PWDT0_IN2                | I2C0_SDA   | UAKIU_KA     | E1O_D4           | 111/011_2/ |

| 37 | 49 | PA10 | GPIO                | PWM2_CH3               | ADC_IN1/ACMP_IN1[1] | PWDT0_IN2  | EIO_D3     | UARTO_RTS  | HIGH_Z |

|----|----|------|---------------------|------------------------|---------------------|------------|------------|------------|--------|

| 38 | 50 | PA11 | GPIO                | PWM2_CH2               | ADC_IN0/ACMP_IN0[1] | PWDT0_IN1  | EIO_D2     | UARTO_CTS  | HIGH_Z |

| 39 | 51 | PC6  | GPIO                | UART1_TX               | Timer_ALT0          | PWDT1_IN2  | CAN0_TX    | PWM1_CH1   | HIGH_Z |

| 40 | 52 | PC7  | GPIO                | UART1_RX               | Timer_ALT1          | PWDT1_IN1  | CAN0_RX    | PWM1_CH0   | HIGH_Z |

|    | 53 | PD5  | GPIO                | SPI0_NSS               | PWM1_CH7            | CAN0_STDBY | UART1_RTS  |            | HIGH_Z |

|    | 54 | PD6  | GPIO                | SPI0_MOSI              | PWM1_CH6            | Timer_ALT2 | UART1_CTS  |            | HIGH_Z |

| 41 | 55 | PC8  | GPIO                | PWM1_CH7               | CAN0_STDBY          | PWDT1_IN0  | CAN1_TX    | PWM2_CH0   | HIGH_Z |

| 42 | 56 | PC9  | GPIO                | PWM1_CH6               | Timer_ALT3          | ACMP_OUT   | CAN1_RX    | PWM2_CH1   | HIGH_Z |

| 43 | 57 | PB9  | GPIO                | PWM1_CH5               | I2C1_SCL            | UART2_TX   | CAN1_STDBY | EIO_D1     | HIGH_Z |

| 44 | 58 | PB10 | GPIO                | PWM1_CH4               | I2C1_SDA            | UART2_RX   | PWDT1_IN0  | EIO_D0     | HIGH_Z |

|    | 59 | PD7  | GPIO                | SPI0_MISO              |                     | SPI1_NSS   | PWM1_FLT1  |            | HIGH_Z |

|    | 60 | PD8  | GPIO                | SPI0_SCK               |                     | SPI1_MOSI  | PWM1_FLT0  |            | HIGH_Z |

| 45 | 61 | PB2  | GPIO <sup>[1]</sup> | NMI_B                  | PWM0_FLT0           | PWDT0_IN0  | PWM2_CH0   | RTC_CLKOUT | HIGH_Z |

| 46 | 62 | PA13 | GPIO                | SWD_CLK[1]             |                     | RTC_CLKOUT | PWM1_CH0   | ACMP_IN9   | HIGH_Z |

| 47 | 63 | PD9  | GPIO                | RESET_B <sup>[1]</sup> |                     |            |            |            | HIGH_Z |

| 48 | 64 | PA14 | GPIO                | SWD_DIO[1]             | ACMP_OUT            | PWM1_CH0   |            |            | HIGH_Z |

<sup>[1]</sup> 该功能为默认功能;

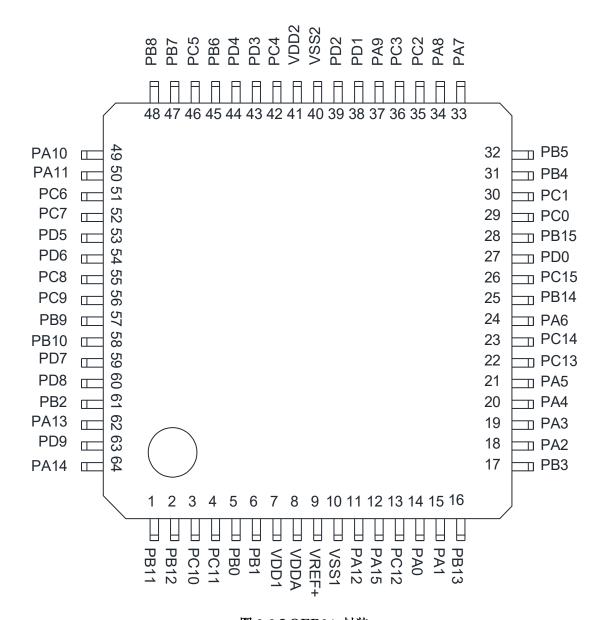

### 9.2 器件引脚分配

图 9-1 LQFP48 封装

图 9-2 LQFP64 封装